32 Bit - Embedded RISC-V Processor Core

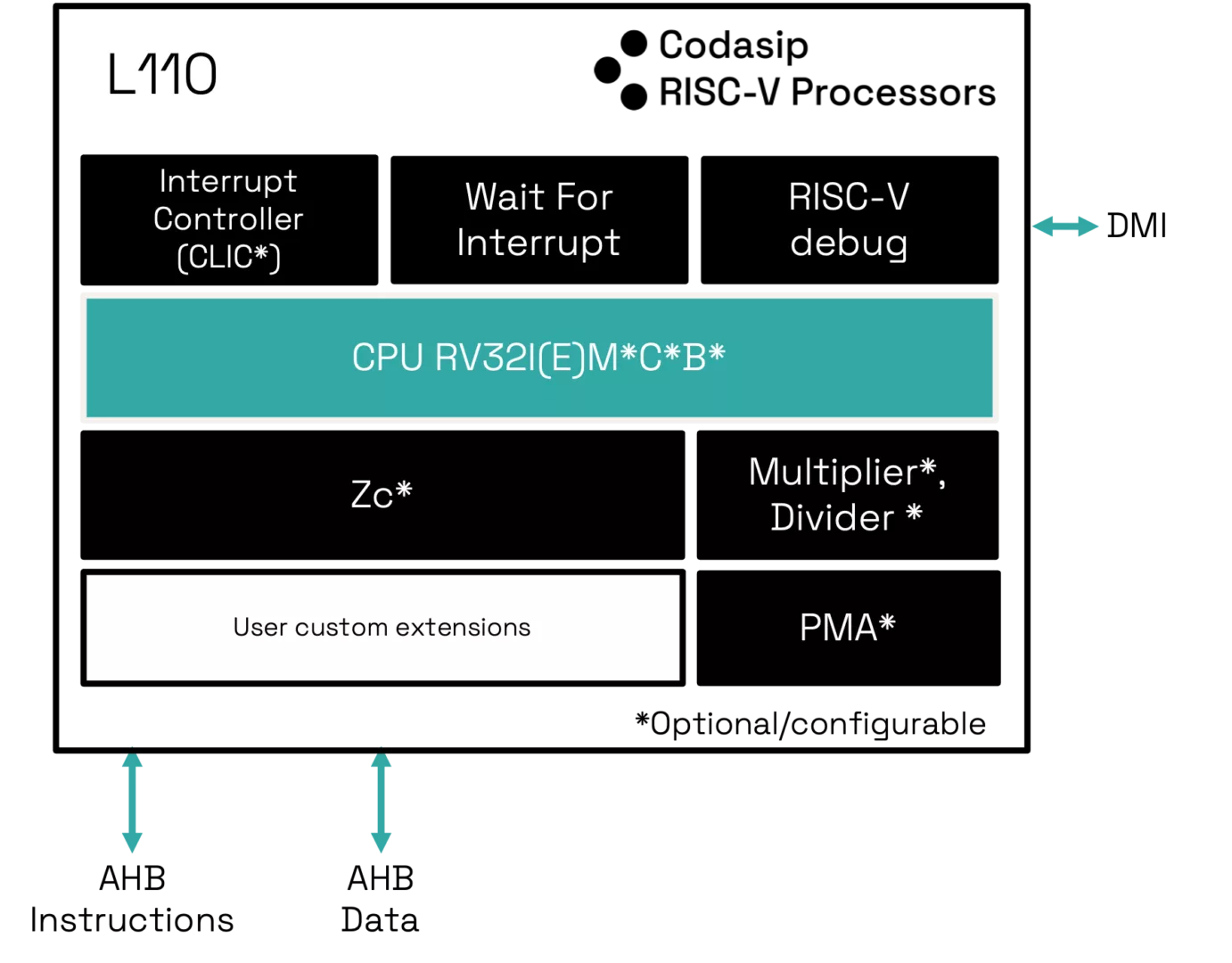

Codasip® L110 is a 32-bit RISC-V embedded processor, focused on small-area and low-power applications.

Overview

Codasip® L110 is a 32-bit RISC-V embedded processor, focused on small-area and low-power applications.

The core is highly configurable, allowing different area and performance levels, with optional support for standard RISC-V code size density extension.

It is also fully customizable, and, when used in combination with Codasip Studio, it enables an easy and no-risk way to add custom instructions.

Key features

- Best-in-class performance for small-area and low-power applications

- Delivering up to 50% improvements in performance per watt compared to similar cores in the market

- Smaller and more performant than other RISC-V alternatives

- Uses RISC-V standard extensions for area and code size reduction for additional power consumption reduction at system level

- Highly configurable and easy and quick to customize and verify

- High-quality pre-verified baseline excellent for further configurations and

- customization

- Easy to customize and verify thanks to Codasip Studio Fusion

- Customization is without risk, because the functionality of the baseline core is guaranteed

- Process compliant with ISO 26262 and ISO 21434

- Developed using HW development process certified by TÜV SÜD

- Development process certified for functional safety as well as cybersecurity

Block Diagram

Benefits

- Ideal standard RISC-V IP for low area and low power applications, competitive in delivering performance per watt.

- Highly configurable with optional support for standard code size density extensions. Excellent base to add custom instructions to further improve power, performance, and area for specific target application

Applications

- Embedded

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is 32 Bit - Embedded RISC-V Processor Core?

32 Bit - Embedded RISC-V Processor Core is a CPU IP core from Codasip listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.