Real PPA improvements from analog IC migration

Analog migration projects live or die on numerous metrics – it is not easy, to say the least. Three very critical metrics are PPA, Performance, Power and Area. Here’s what most analog designers already know: when you’re porting IP to a new process, the real goal isn’t improvement—it’s preservation. You want to maintain performance specifications while adapting to the new technology. Yet while anything beyond that is technically a bonus, those additional benefits are often demanded as part of the business case for migration in the first place.

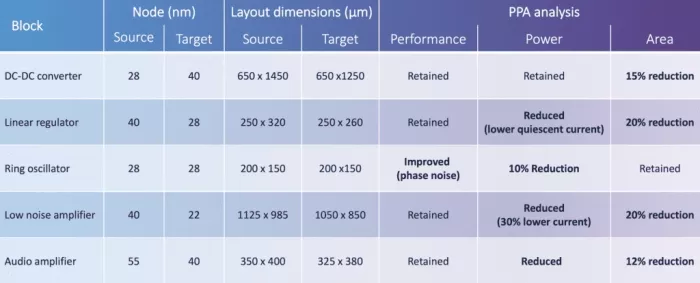

We’ve been working with design teams on analog IP migration for over a decade. Rather than make broad claims about guaranteed improvements, here’s what we’ve measured across five recent migration projects and what the original expectations were versus what we achieved.

Figure 1 : PPA improvements achieved using AMALIA Platform

Early prediction of area changes

AMALIA can predict area changes during circuit porting, which happens immediately after technology analysis—essentially the first step of migration. Before you’ve invested time in layout work, you get an estimate of whether area will increase, decrease or remain constant.

What these results tell us

First, these aren’t guaranteed outcomes. PPA results depend on many factors: the differences in device characteristics between source and target PDKs, the variations in DRC rules and spacing requirements between foundries (even at the same nominal node size), and critically, the design itself—how it was originally architected to achieve its intended functionality, performance and power requirements.

Second, customer expectations are revealing. In every case, the primary requirement was performance. Customers said: “Maintain my specifications—or better yet, improve them. Area and power matter, but not if performance suffers.” The fact that most migrations also delivered area and power improvements reflects both the quality of the original designs and the optimization opportunities that AMALIA identified during porting.

Third, some improvements are process-inherent, others are optimization results. When you move to a smaller node with better transistor models, you might achieve the same gain with lower current—that’s the process helping you. When you reduce area by 15% while moving to a larger node, that’s optimization finding efficiencies.

The practical takeaway

If you’re evaluating automated migration, set your expectations based on your primary requirement. If that’s performance preservation, that’s achievable across node transitions and foundry changes. Area and power improvements are realistic secondary outcomes, particularly when moving to smaller nodes or better-matched process variants.

With the AMALIA Platform we have experienced see area reductions in the 10-30% range when geometry scaling is favorable. Power improvements depend on whether your circuit can exploit better transistor characteristics at the target node and examples driven by AMALIA Platformhave achieved reductions of 10—35%. In all migrations, results always depend on many factors not least those affected by the source and target process technologies

The question is not if automation delivers perfect results. It’s if starting with performance preservation as the baseline, with early visibility into likely PPA changes, gives you better outcomes than manual migration. Based on these projects—and the fact that customers keep coming back for their next migration—the answer appears to be yes with Thalia technology.

Related Semiconductor IP

- SHA-256 Secure Hash Algorithm IP Core

- EdDSA Curve25519 signature generation engine

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

- LunaNet AFS LDPC Encoder and Decoder IP Core

Related Blogs

- The REAL Cost for a Custom IC

- Applied AI in Analog IC Design Migration

- The Hidden Threat in Analog IC Migration: Why Electromigration rules can make or break your next tapeout

- Mixed Signal Success Requires the Voice of Analog Designers

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk