Powering Up Efficiency: A Deep Dive into CXL L0p and its Verification

Compute Express Link (CXL) is revolutionizing data center architecture, with power management emerging as a key area of innovation. Among its power-saving mechanisms, the L0p (Low Power) state plays a pivotal role in reducing energy consumption during periods of low link activity. But what exactly does L0p mean for a CXL link, and how can we ensure its reliable implementation through comprehensive verification?

Understanding CXL L0p: The Path to Power Efficiency

L0p (short for "Low Power") is a specialized sub-state of the L0 operational state in which the CXL link maintains partial lane activity. In this mode, some lanes remain active while the others transition to an electrical idle state. This is achieved by dynamically adjusting the link width—downsizing to use fewer lanes during low demand, and upsizing to utilize more lanes when demand increases. Despite these adjustments, the link remains fully operational within the L0 state, ensuring efficient power management without compromising performance.

How L0p Works

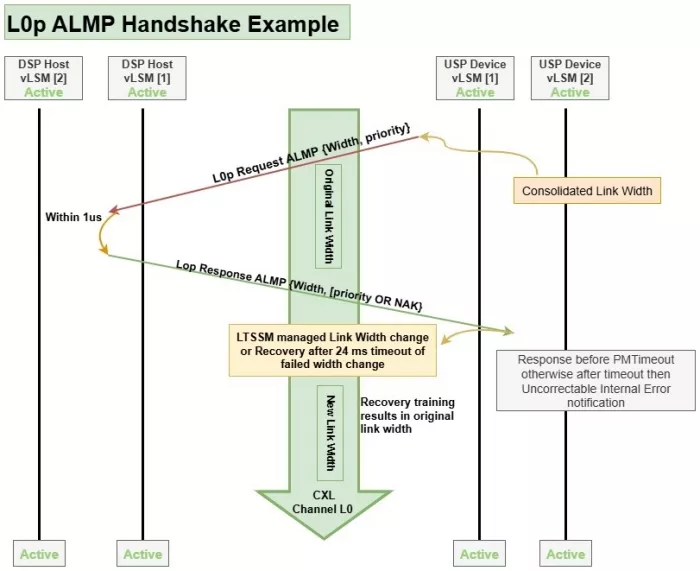

- Initiation: Either side (root or endpoint) can initiate a lane width change.

- Negotiation: A new L0p ALMP packet is used to send a request (e.g., downsize from x8 to x4).

- Acknowledgment: The partner device responds with L0p ALMP ACK or NAK within a defined time (e.g., 1 µs).

- Lane transition:

- Downsizing: Inactive lanes send EIOSQ and go to electrical idle.

- Upsizing: New lanes are trained and brought online.

- Traffic continuity: Active lanes continue transmitting FLITs during the transition.

The Verification Challenges: Making Sure L0p Always Works

Making sure CXL's L0p feature works perfectly, especially with dynamic link width adjustments, comes with a few tricky parts:

- Complex steps and width changes: Entering and exiting the L0p (Low Power) state involves a series of precise operations, now further complicated by the dynamic addition or removal of active data lanes. These transitions must be validated across all aspects of the CXL link—including data handling, link integrity, and physical layer signaling—to ensure seamless and error-free operation.

- Power efficiency vs. performance trade-off: It is essential to verify that L0p mode delivers meaningful power savings by adjusting link width, without introducing significant latency or performance degradation during bandwidth ramp-up. This is particularly critical under fluctuating data traffic conditions, where responsiveness and efficiency must be balanced.

- Cross-layer coordination: Robust validation is required to ensure that all protocol layers—Transaction Layer, Link Layer, ArbMux, and Physical Layer—operate in harmony during L0p transitions. Any misalignment or delay across layers could compromise link stability or performance.

- Fault handling and recovery scenarios: Testing must cover fault conditions such as errors, resets, or unexpected state changes during L0p operation. Special attention should be given to recovery entry and transitions into deeper power states, ensuring that the link can gracefully handle disruptions and resume normal operation without data loss or corruption.

How Verification IP (VIP) Makes Testing L0p Easy

CXL Verification IP (VIP) is a super helpful tool for tackling these challenges:

- Configurable L0p scenarios with dynamic link width control: CXL VIP enables engineers to easily configure and execute a wide range of L0p scenarios, including precise control over link width scaling—both downsizing and upsizing. This allows for thorough validation of component behavior during dynamic lane transitions.

- Protocol-aware error detection: Equipped with intelligent protocol monitoring, the VIP automatically detects violations in L0p operations, such as incorrect negotiation sequences or non-compliant link width transitions. This significantly reduces manual debugging effort and accelerates issue identification.

- Fault Injection during transitions: The VIP supports targeted error simulation during L0p transitions, including injecting unexpected protocol messages or faults during lane reduction or expansion. These tests help assess system robustness and recovery mechanisms under adverse conditions.

- Performance and power efficiency analysis: Advanced metrics provided by the VIP allow for detailed analysis of L0p entry/exit latency, link width transition efficiency, and associated power consumption. These insights are critical for optimizing power-saving strategies without compromising performance.

- Comprehensive coverage across scenarios: CXL VIP offers exhaustive test coverage for all L0p-related conditions—ranging from varying traffic loads and dynamic link width changes to error recovery paths. This ensures high confidence in the reliability and efficiency of L0p implementation.

Conclusion

By using CXL VIP, teams can confidently build and test the clever L0p power-saving feature, including its dynamic link width capabilities. This means CXL systems will not only be fast but also incredibly energy-efficient for the powerful computing systems of today.

Learn More

Related Semiconductor IP

- CXL 4 Verification IP

- VIP for Compute Express Link (CXL)

- CXL 3.0 Controller

- CXL Controller

- CXL 4.0/3.2/3/2 Verification IP

Related Blogs

- Embracing the Future with Cortex-A320: A Deep Dive into the General Armv9 Architecture Adoption

- Trust at the Core: A Deep Dive into Hardware Root of Trust (HRoT)

- Scalable I/O Virtualization: A Deep Dive into PCIe’s Next Gen Virtualization

- Unlock Your AI Potential: A Deep Dive into BrainChip’s Akida™ Cloud

Latest Blogs

- Enabling Memory Choice for Modern AI Systems: Tenstorrent and Rambus Deliver Flexible, Power-Efficient Solutions

- Verification Sanity in Chiplets & Edge AI: Avoid the “Second Design” Trap

- Embedded Security explained: Cryptographic Hash Functions

- Arm and Google Cloud redefine agentic AI infrastructure with Axion processors

- A Bench-to-In-Field Telemetry Platform for Datacenter Power Management