Maximizing the Usability of Your Chip Development: Design with Flexibility for the Future

Early in my career selling chips for Motorola Semiconductor, the ability to spin derivative microcontroller chips for a customer’s specific requirement was relatively straightforward. If the volume looked reasonable, we would tape-out a new chip with a few added features because mask costs and wafers were relatively inexpensive at the larger process nodes. The customer won by getting an MCU tailored to their specific need, and Motorola won by gaining a more committed customer plus another SKU that could be sold to other customers – boosting ROI.

With the migration to higher cost FinFET nodes, those times are long gone as the economics no longer work. Semiconductor companies need to see tens of millions of dollars, if not hundreds of millions of dollars of revenue before embarking on a new chip tape-out. This leaves small to mid-sized companies with little ability to influence product roadmaps for their needs and constrained to use whatever Commercial Off-the-Shelf (COTS) chips are available which leads to higher overall costs because they are forced to buy more compute resources and features than they need or have to supplement the MCU with an FPGA companion chip.

High volume mobile handset companies and high intensity compute data center companies ran into this issue years ago because they could no longer rely on merchant semiconductor companies to satisfy their unique compute requirements. So, they took control of their own hardware and processor roadmaps in order to have full control over their hardware and software destiny. More companies are now adopting this model because of the supply chain issues they experienced during the pandemic so they can have direct control over their silicon supply chain as well as to protect their hardware and software future.

As a product planner, what can you take away from these trends to maximize the return on product investment? Build as much flexibility into your processing chip as you can. This is precisely where embedded FPGA (eFPGA) IP comes in. Simply put, eFPGA IP is essentially integrating a small FPGA chip into strategic locations within your SoC to provide the ability to make circuit changes in the SoC which can be done prior to shipment or in the field. Not sure how you can leverage this type of IP? Here are three common use cases being used today:

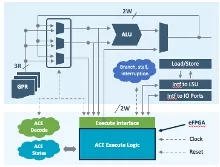

Accelerators and co-processors for algorithms that are more efficiently run in dedicated hardware versus on an embedded CPU. Dedicated accelerators are well proven to save power by dramatically reducing CPU cycles for heavy and parallel processing workloads. Utilizing eFPGA for custom instructions and co-processors as supported by today’s mainstream popular processors, allows you to build upon the base processor platform and provide custom compute for various and different workloads thereby enabling your SoC to be used in adjacent applications and markets. This concept also applies to system companies whose end users may benefit from dedicated hardware assist for the CPU. A classic example of this is the use of ARC processors with custom instructions used in game cartridges for Super Nintendo. Except now with eFPGA, the user doesn’t need a unique chip for each game cartridge, they can simply upload game-specific instruction as a bit stream which improves performance and enhances the user’s gaming experience.

Accelerators and co-processors for algorithms that are more efficiently run in dedicated hardware versus on an embedded CPU. Dedicated accelerators are well proven to save power by dramatically reducing CPU cycles for heavy and parallel processing workloads. Utilizing eFPGA for custom instructions and co-processors as supported by today’s mainstream popular processors, allows you to build upon the base processor platform and provide custom compute for various and different workloads thereby enabling your SoC to be used in adjacent applications and markets. This concept also applies to system companies whose end users may benefit from dedicated hardware assist for the CPU. A classic example of this is the use of ARC processors with custom instructions used in game cartridges for Super Nintendo. Except now with eFPGA, the user doesn’t need a unique chip for each game cartridge, they can simply upload game-specific instruction as a bit stream which improves performance and enhances the user’s gaming experience.

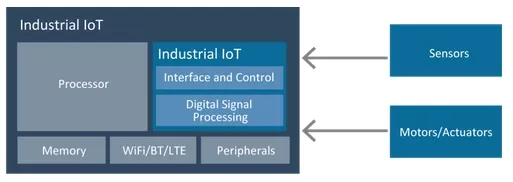

IO Flexibility: Being able to connect your chip to any other chip or device, be it a new processing platform, camera, touchscreen, fingerprint recognition or even a data converter, provides the opportunity to win more sockets, get more revenue and improve ROI. eFPGA IP is constructed of Look-Up Tables (LUTs), and only a few hundred LUTs are all that is needed to be able to support more customers and applications with a single SKU. Case in point is the adoption of I3C. For decades, I2C was the de facto chip-to-chip serial communication interface. I3C was developed to handle moving vastly more data generated by the latest sensors. Sensor data collection will continue to increase which means the algorithms and protocols to manage the data will need to evolve as well. eFPGA in the peripheral space can help you evolve the on-chip peripherals without needing to spin derivatives like in my old Motorola days.

IO Flexibility: Being able to connect your chip to any other chip or device, be it a new processing platform, camera, touchscreen, fingerprint recognition or even a data converter, provides the opportunity to win more sockets, get more revenue and improve ROI. eFPGA IP is constructed of Look-Up Tables (LUTs), and only a few hundred LUTs are all that is needed to be able to support more customers and applications with a single SKU. Case in point is the adoption of I3C. For decades, I2C was the de facto chip-to-chip serial communication interface. I3C was developed to handle moving vastly more data generated by the latest sensors. Sensor data collection will continue to increase which means the algorithms and protocols to manage the data will need to evolve as well. eFPGA in the peripheral space can help you evolve the on-chip peripherals without needing to spin derivatives like in my old Motorola days.

Hiding your “secret sauce”: Lastly, if you have customers or 3rd parties writing software to program your chip, allowing them access to the eFPGA means they have another avenue to differentiate by adding their own proprietary RTL IP. Also known as obfuscation, the proprietary code is never shared – it is only programmed at a location of their choosing: pre-shipment, in system or even in the field. Obfuscation can also help avoid export license hassles if those designs are subject to export control or ITAR restrictions. This is accomplished by shipping the unprogrammed eFPGA to the region where it will be put into operation and programming there.

Hiding your “secret sauce”: Lastly, if you have customers or 3rd parties writing software to program your chip, allowing them access to the eFPGA means they have another avenue to differentiate by adding their own proprietary RTL IP. Also known as obfuscation, the proprietary code is never shared – it is only programmed at a location of their choosing: pre-shipment, in system or even in the field. Obfuscation can also help avoid export license hassles if those designs are subject to export control or ITAR restrictions. This is accomplished by shipping the unprogrammed eFPGA to the region where it will be put into operation and programming there.

There’s a reason why AMD MPSoC and Altera’s SoC FPGAs are popular. They combine the benefits of software programmability with circuit reconfigurability. The downside to these FPGA SoCs is that you are paying for all their features whether you are using them or not, or they don’t support the processing you need, and must supplemented with a companion chip.

QuickLogic’s eFPGA hard IP generated by their proprietary Australis automation tool means the chip designer has the freedom to put in as much logic (LUTs), DSP cores and BlockRAMs to suit their specific needs. To help with architecture exploration, QuickLogic’s Aurora FPGA User Tool is used to find the right balance of resources which is used by Australis to generate a custom hard eFPGA IP that’s right sized to minimize area impact. The result is a personalized MPSoC that has the right ASIC compute and eFPGA resources tailored for your needs.

In closing, if your product’s success is really saying you should move to an ASIC to save costs or be in control of your hardware roadmap and supply chain while protecting your software investment, you can get exactly what you need with your ASIC and by including eFPGA, be positioned to win more business, lower costs and improve your ROI.

Related Semiconductor IP

- Radiation-Hardened eFPGA

- eFPGA Hard IP Generator

- eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

- Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

- eFPGA on GlobalFoundries GF12LP

Related Blogs

- Building Smarter, Faster: How Arm Compute Subsystems Accelerate the Future of Chip Design

- Driving the Future of High-Speed Computing with PCIe 7.0 Innovation

- UEC-LLR: The Future of Loss Recovery in Ethernet for AI and HPC

- Cadence at the TSMC OIP: Pioneering the Future of Semiconductor Design

Latest Blogs

- A Bench-to-In-Field Telemetry Platform for Datacenter Power Management

- IDS-Verify™: From Specification to Sign-Off – Automated CSR, Hardware Software Interface and CPU-Peripheral Interface Verification

- RISC-V and GPU Synergy in Practice: A Path Towards High-Performance SoCs from SpacemiT K3

- EDA AI Agents: Intelligent Automation in Semiconductor & PCB Design

- Why Security Can't Exist Without Trust