An Overview of CXL Mode Alternate Protocol Negotiation

The Peripheral Component Interconnect Express (PCIe) protocol has a very powerful feature called Alternate Protocol Negotiation (APN), which was introduced in the PCIe 5.0 specification. This feature allows the alternate protocols (non-PCIe) that use PCIe PHY layer to be enabled and provide their own implementation of the more abstract layers.

One of the most common alternate protocols is the Compute Express Link (CXL), which provides a high-bandwidth, low-latency communication with cache coherency, memory sharing, and I/O support. CXL includes three sub-protocols: CXL.io, CXL.cache, and CXL.mem.

Understanding PCIe Alternate Protocol Negotiation

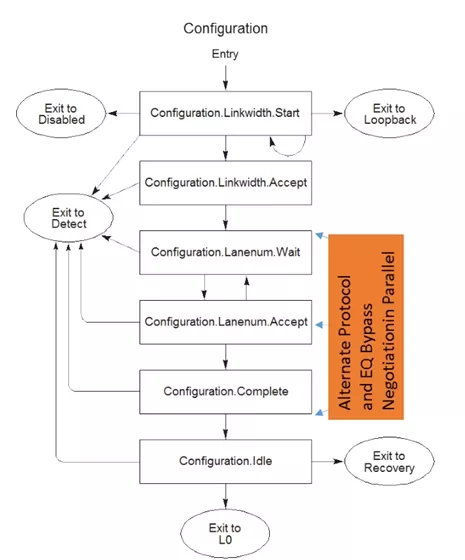

While the PCIe link is being trained, the devices are allowed to negotiate an alternate protocol during three of the Link Training Status State Machine (LTSSM) states:

- Configuration.Lanenum.Wait: Proposes lane numbers for each lane of the link.

- Configuration.Lanenum.Accept: Confirms the lane number of each lane of the link.

- Configuration.Complete: Makes sure that the link configuration is correct.

This involves exchanging modified training sets (TS1/TS2) using 8b/10b encoding mechanism, with support for other encodings like 128b/130b.

Figure 1. Configuration LTSSM states transition diagram

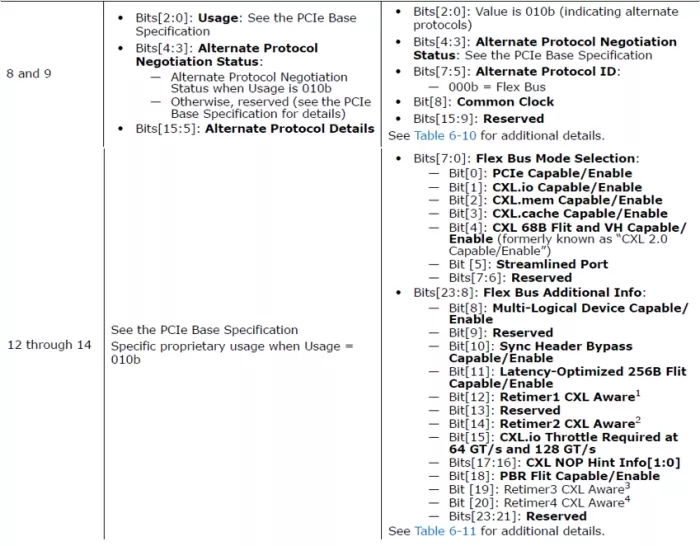

The modified training sets are modified versions of the standard PCIe training set, containing APN-specific data from symbols 8 to 14, with fields modified TS info 1 (symbols 8 - 9) and Info 2 (symbols 12 - 14). If the modified training sets are not supported, the link will operate in PCIe mode. The meanings of the symbols are determined by the alternate protocol being negotiated.

Figure 2. APN-specific symbol meanings

Diving into CXL Alternate Protocol Negotiation

By using the APN mechanism explained previously, CXL can be negotiated if both devices support CXL. This is known as Flex Bus.CXL mode negotiation, as it happens on a flex bus port.

The negotiation happens during the configuration states before entering L0 at 2.5 GT/s, but once negotiation completes and the link reaches final speed, it must reach 8.0 GT/s or higher. If link fails to transition to those higher speeds, then the link-up will ultimately fail. Flex Bus.CXL mode requires the link to be constantly above this limit speed, and if speed drops below this threshold and fails to recover, LTSSM transitions to Detect state.

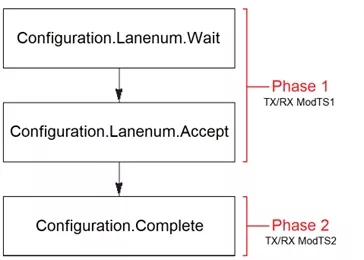

Flex Bus.CXL Mode APN is divided into two main phases: phase 1 and phase 2. LTSSM state transitions still follow PCIe rules.

Figure 3. Phase 1 and Phase 2 overview

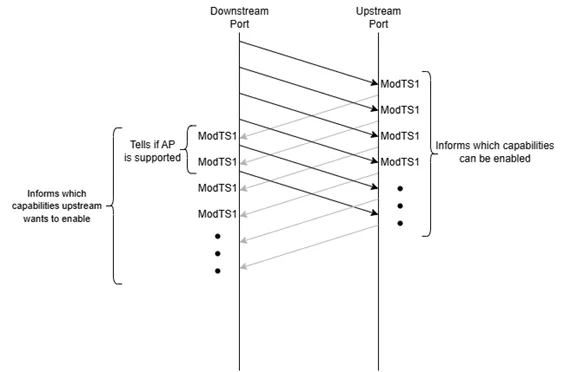

Phase 1

Happens during Configuration.Lanenum.Wait and Configuration.Lanenum.Accept.

Figure 4. ModTS1 exchange flow in phase 1

Phase 2

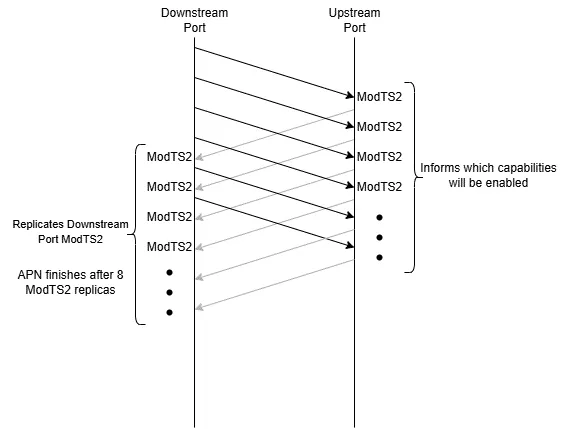

Happens during Configuration.Complete.

Figure 5. ModTS2 exchange flow in phase 2

If the downstream port receives a different combination of the Flex Bus bits than what it transmitted, LTSSM returns to detect state. And if the upstream port receives any combination that is not a subset of what is advertised in phase 1, the behavior is undefined.

After the Negotiation

As soon as the eight modified TS2s with flex bus capabilities replicas are received by the downstream port, the APN is finished successfully, and the upper layers are allowed to be informed of the results of the exchange. However, the CXL features are only allowed to be enabled after the LTSSM goes to L0 at a speed of at least 8 GT/s.

APN Challenges and VIP Solutions

The fact that the alternate protocol negotiation can happen in parallel with lane number negotiation and decision to skip equalization can complicate debugging when investigating the behavior of a device. Besides, checking the data on Modified TS1/2 to see the features that the instances want to enable can be quite time consuming, as it would require looking into a stream of bits and comparing with what the specification says.

To solve this issue and facilitate a better understanding of the process, VIP implements various mechanisms to help the user and to make the debug process smoother. These are some of them:

- Internal APN state tracking: Helps understand what is expected from each device at any moment in time, such as what kind of packets are to be transmitted and which LTSSM state it should be on.

- Error checkers: If a device sends unexpected data, VIP will immediately fire an error message explaining the failure and what is expected according to the specification.

- Trace generation: Every relevant information can also be logged into a file to make visual inspection easy, some of which are, but not limited to: timestamps, state machine changes, packet data and direction, debug messages, etc.

Conclusion

In summary, the Alternate Protocol Mechanism is a straightforward, but very powerful, mechanism from the PCIe specification that allows great flexibility of operation modes and protocol-specific implementations. CXL takes advantage of that to provide its own abstractions for the data coming from the PHY layer, making it possible to achieve high bandwidths following all the optimizations for a fast transfer rate provided by PCIe. By using a simple approach of exchanging Modified Training Sets with the supported capabilities, CXL can provide great compatibility between devices that support different features.

Cadence’s VIP gives the user ease of access to every relevant aspect of the APN, making the process of investigating device behavior direct and as simple as possible. This reduces time spent on debugging and makes it less error-prone by automating error checking.

More Information

- For more information about how Cadence PCIe/CXL Verification IP and TripleCheck enable users to confidently verify disruptive changes, see Simulation VIP for CXL, Simulation VIP for PCIe, and TripleCheck for PCIe and CXL

- For the press release on CXL3.0, please read Cadence's CXL 3.0 Verification IP Press Release

- For more information on CXL in general, please visit the CXL Consortium website

- If you have more feedback or need more information, reach out to us at talk_to_vip_expert@cadence.com

Related Semiconductor IP

- Simulation VIP for CXL

- Controller for CXL

- CXL 4 Verification IP

- VIP for Compute Express Link (CXL)

- CXL 3.0 Controller

Related Blogs

- Leveraging the PCIe for CXL Mode Link Up Using Alternate Protocol Negotiation Technique

- De-mystifying CXL: An overview

- Evolution of AMBA AXI Protocol: An Introduction to the Issue L Update

- Arasan In Year 2013 - 2014 - An Overview

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk