Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

As AI workloads grow in scale and complexity, networks are challenged to keep up. According to McKinsey & Company, global demand for data center capacity is projected to nearly triple by 2030, with AI workloads expected to account for approximately 70% of that increase. GPT-5 reportedly will have 17 trillion parameters, which would represent a 10X increase over GPT-4. In addition, in its "2024 United States Data Center Energy Usage Report," Lawrence Berkeley National Laboratory projects 200/400Gb ports will grow from 6% to 26% of network energy share by 2028. To address these trends, AI infrastructure must be scalable to easily accommodate tomorrow's AI models, and scalable, efficient AI factories and hyperscale data centers begin with innovative IP.

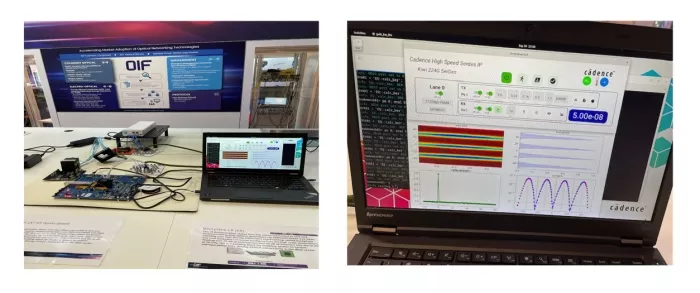

At the recent ECOC 2025 conference in Copenhagen, Cadence showcased its key role in enabling the future of AI infrastructure with live silicon demonstrations of several essential IP technologies for emerging 800G and 1.6T networks. Powered by Cadence's 224G SerDes IP, Cadence's Ultra Accelerator Link (UALink 1.0) scale-up and Ultra Ethernet scale-out networking solutions deliver the performance, flexibility, and interoperability needed for next-generation AI factories and hyperscale data centers.

With the rise of new industry-standard protocols like UALink and Ultra Ethernet, seamless connectivity and interoperability between the various networking system components, including cables, connectors, and optical technologies, is crucial.

Live Demos: Real-World Performance

Real-world demonstrations at events like ECOC validate that high-speed IP, such as the Cadence 224G SerDes, perform as intended over both long and short reach with optimal signal integrity, low latency, and low power consumption. Cadence's live silicon demos of its 224G SerDes PHY IP highlighted its robustness, interoperability, and technical excellence in real-world scenarios featuring ecosystem vendors' cable and connector solutions.

At the OIF booth at ECOC, Cadence showcased CEI-224G-LR interoperability at a data rate of 212.5Gbps with a PRBS31Q data pattern, with total insertion loss exceeding 40dB (bump to bump) at Nyquist frequency. The long-reach 224G PHY demo setup featured a Multilane transmitter to Cadence receiver test chip silicon and cabled backplane channels using a Samtec SiFly HD connector with a 1m cable and a TE near-chip connector with backplane connectors and TE cables. The successful demo achieved a pre-FEC bit-error rate (BER) of 5E-08, highlighting the solution's error-free performance under demanding conditions.

At the Cadence booth, Cadence demonstrated serial link performance with a 45dB channel insertion loss (bump to bump) at a 212.5Gbps data rate and PRBS31Q data pattern, with a Cadence transmitter to receiver link setup. The achieved pre-FEC BER was 4E-08, further validating the robustness of the 224G PHY link setup. In a full solution with FEC, the system operates nearly error-free.

Technical Takeaways

- Robustness: Both demos prove Cadence's 224G PHY can maintain high data integrity and low error rates over extremely challenging channels.

- Interoperability: The use of industry-standard connectors and cables ensures seamless integration with other ecosystem solutions, which is critical during a rapid AI infrastructure build out.

- Scalability: The technology supports full-duplex operation from 1.25Gbps to 225Gbps, enabling future-proof deployments for 1.6T, 800G, 400G, and 200G Ethernet networks.

- Design Flexibility: The beachfront-optimized floorplan allows flexible SoC edge placement, and the PHY supports chip-to-module (VSR), chip-to-chip (MR), and copper/backplane (LR) interconnects.

Scaling Up and Scaling Out: UALink and Ultra Ethernet

Cadence's multiprotocol PHYs support both 112G and 224G operation over long and short reach and across process nodes from 7nm down to 2nm+, ensuring future-proof scalability. Optimized and configurable controller options allow tailored solutions for specific application needs, maximizing efficiency and interoperability. Cadence controllers support best-in-class UALink 1.0 and Ultra Ethernet, as well as standard Ethernet, CPRI, and JESD protocols. Cadence's Ultra Ethernet controller supports the most versatile protocol features, ensuring compatibility with evolving IEEE and OIF standards.

Cadence: A Trusted IP Partner for AI/HPC

Cadence's commitment to enabling ecosystem interoperability and leading the future of high-speed connectivity with UALink and Ultra Ethernet innovation was evident at ECOC 2025. These protocols are not only meeting today's connectivity challenges, they are also paving the way for the next generation of AI, high-performance computing (HPC), and hyperscale data center networks.

Modern AI infrastructure demands more than legacy solutions. When scaling AI to meet today's and tomorrow's power, performance, and area demands, you need a trusted partner with a broad portfolio of solutions optimized for the AI/HPC market. Cadence has the expertise and proven IP to help you optimize throughput, balance power and performance, and solve your networking, memory, and chiplet connectivity challenges.

Learn more about how Cadence's 224G SerDes, UALink, and Ultra Ethernet solutions are setting a new benchmark for scaling up and scaling out next-generation AI factories by visiting the 224G-LR SerDes PHY landing page.

Related Semiconductor IP

Related Blogs

- Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

- Cadence Perspective: 224G SerDes Trend and Solution

- Ultra Ethernet Consortium Set to Enable Scaling of Networking Interconnects for AI and HPC

- Ultra Ethernet Security: Protecting AI/HPC at Scale

Latest Blogs

- A Bench-to-In-Field Telemetry Platform for Datacenter Power Management

- IDS-Verify™: From Specification to Sign-Off – Automated CSR, Hardware Software Interface and CPU-Peripheral Interface Verification

- RISC-V and GPU Synergy in Practice: A Path Towards High-Performance SoCs from SpacemiT K3

- EDA AI Agents: Intelligent Automation in Semiconductor & PCB Design

- Why Security Can't Exist Without Trust