CVA6-CFI: A First Glance at RISC-V Control-Flow Integrity Extensions

By Simone Manoni 1, Emanuele Parisi 2, Riccardo Tedeschi 1, Davide Rossi 1,3, Andrea Acquaviva 1, Andrea Bartolini 1

1 Department of Electrical, Electronic, and Information Engineering - University of Bologna, Italy

2 High Performance Domain-Specific Architectures Group - Barcelona Supercomputing Center, Spain

3 Department of Digital Design and Open Hardware - Chips-IT, Italy

Abstract

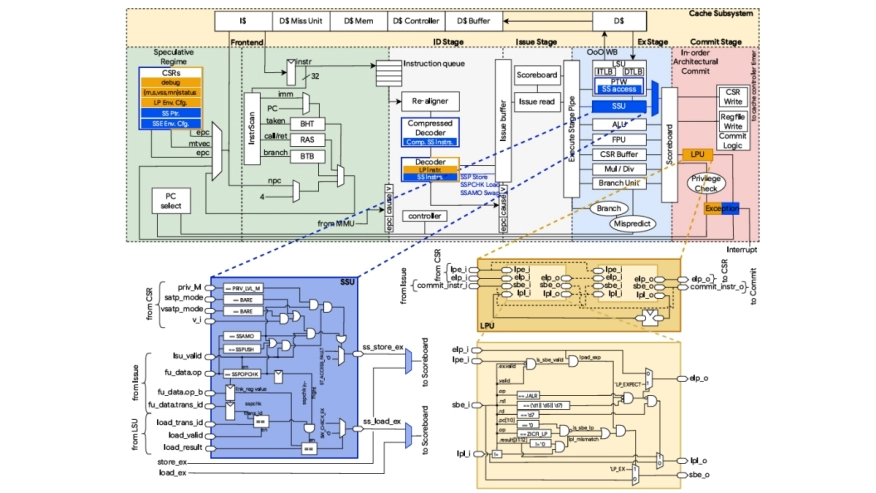

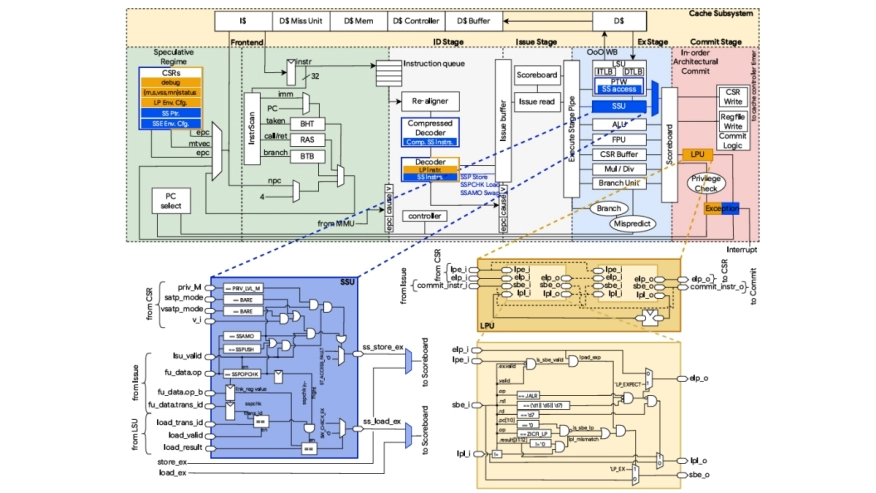

This work presents the first design, integration, and evaluation of the standard RISC-V extensions for Control-Flow Integrity (CFI). The Zicfiss and Zicfilp extensions aim at protecting the execution of a vulnerable program from control-flow hijacking attacks through the implementation of security mechanisms based on shadow stack and landing pad primitives. We introduce two independent and configurable hardware units implementing forward-edge and backward-edge control-flow protection, fully integrated into the open-source CVA6 core. Our design incurs in only 1.0% area overhead when synthesized in 22 nm FDX technology, and up to 15.6% performance overhead based on evaluation with the MiBench automotive benchmark subset. We release the complete implementation as open source.

This work presents the first design, integration, and evaluation of the standard RISC-V extensions for Control-Flow Integrity (CFI). The Zicfiss and Zicfilp extensions aim at protecting the execution of a vulnerable program from control-flow hijacking attacks through the implementation of security mechanisms based on shadow stack and landing pad primitives. We introduce two independent and configurable hardware units implementing forward-edge and backward-edge control-flow protection, fully integrated into the open-source CVA6 core. Our design incurs in only 1.0% area overhead when synthesized in 22 nm FDX technology, and up to 15.6% performance overhead based on evaluation with the MiBench automotive benchmark subset. We release the complete implementation as open source.

Index Terms — Control-Flow Integrity, Shadow Stack, Landing Pad, RISC-V

To read the full article, click here

Related Semiconductor IP

- RISC-V IOPMP IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- 64-bit RISC-V core with in-order single issue pipeline. Tiny Linux-capable processor for IoT applications.

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

Related Articles

- A closer look at security verification for RISC-V processors

- What is JESD204C? A quick glance at the standard

- OpenAccess: first impressions at AMD

- Inside the Xilinx Kintex-7 FPGA: A closer look at the first FPGA to use HKMG technology

Latest Articles

- RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

- Emulation-based System-on-Chip Security Verification: Challenges and Opportunities

- A 129FPS Full HD Real-Time Accelerator for 3D Gaussian Splatting

- SkipOPU: An FPGA-based Overlay Processor for Large Language Models with Dynamically Allocated Computation

- TensorPool: A 3D-Stacked 8.4TFLOPS/4.3W Many-Core Domain-Specific Processor for AI-Native Radio Access Networks