New BA20 Processor IP Features "Zero-Stage Pipeline" for Energy and Performance Efficiency

PipelineZero Architecture, hazards-free single-cycle execution, extreme code density, small silicon area, and power-saving design yield one of the most performance- and energy-efficient 32-bit processors available

Linley Processor Conference, Santa Clara, CA -- October 22 2014 --Wearable devices, Internet of Things (IoT) sensors, and other mobile products challenge the limits of modern processor efficiency, with features requiring significant processing capability but also demanding ultra-low energy consumption. A new 32-bit processor announced today by Beyond Semiconductor and CAST Inc. meets this challenge by combining state-of-the-art design techniques with an architectural feature seemingly drawn from the past: a zero-stage execution pipeline the companies call the PipelineZero™ Architecture.

The new BA20™ PipelineZero 32-bit Embedded Processor IP Core is designed specifically for the most power-sensitive systems, where the usual low-power processor techniques fall short of reaching power targets. Operating at high efficiency with no wasted cycles and maximizing the work accomplished per energy consumed, the BA20 is a new sweet-spot processor for applications not requiring the high operating frequency of modern three- or five-stage pipelined processors. It delivers extremely competitive results for these applications, featuring:

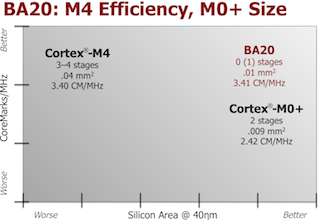

- Competitive Performance Efficiency: 3.04 DMIPS/MHz and 3.41 CoreMarks/MHz

- Small Silicon Area: 0.01mm2 in a 9-track 40G process, and

- Low Power Consumption: 2µW/MHz in the same process technology.

Beyond Semiconductor achieved these results through design techniques already proven in the BA2X™ Processor Family combined with rigorous fine-grained optimizations to minimize switching plus the unique PipelineZero microarchitecture.

Compared to the popular processor line from ARM Ltd., the BA20 Processor provides efficiency comparable to the Cortex®-M4, but with a small size similar to the Cortex®-M0+.

The BA20 Processor offers true single-cycle instruction execution of the BA2™ Instruction Set, which reduces system-wide power usage through industry-leading extreme code density. The processor’s high level of performance efficiency means it can save energy by doing more in less time—sleeping for more of the time—and by operating at lower clock rates. Built-in support for advanced power management techniques such as power and clock gating and dynamic frequency scaling further reduce energy consumption.

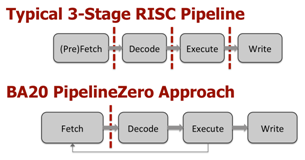

The BA20’s PipelineZero Architecture provides zero-delay branches and no pipeline-stalling overheads. It:

- Eliminates hazards (data, structural, and branch) for higher performance efficiency;

- Has fewer pipeline registers—requiring a minimal number of flip-flops—and a simplified CPU control for smaller area; and

- Has a shorter branch shadow for less wasted energy.

The BA20’s PipelineZero Architecture uses a zero-stage execution pipeline that offers greater performance efficiency than typical multi-stage processors.

Designers can optionally augment the processor’s capabilities with a hardware multiplier/divider, a multiply-accumulate block, and IEEE-754 compliant floating-point units. A vectored interrupt controller facilitates timely responses to interrupts, and an optional memory protection unit protects application code and/or data from corruption. The core’s system interface uses a 32-bit wide AMBA® AXI4-lite bus. Two tightly-coupled embedded memory (EMEM) buses allow fast access for time-critical code and data, and can be used for inter-core communication in a multi-core architecture.

The royalty-free BA20 Processor IP Core is available now in RTL source code or FPGA netlists, complete with the BeyondStudio™ Eclipse-based IDE. Various pre-integrated peripherals, memory controllers, and interconnects are available, as are a non-intrusive JTAG or serial debug package and ready-to-run reference design boards.

Attendees of the Linley Processor Conference can learn more about the new BA20 Processor in a presentation by CAST’s Bill Finch at 1:20 pm on October 22, 2014.

To learn more about CAST and its line of IP cores and subsystems, call +1 201.391.8300, visit www.cast-inc.com. Access further information on Beyond Semiconductor by visiting www.beyondsemi.com.

Related Semiconductor IP

- Real-time Pixel Processor for Vision applications

- 64-bit RISC-V core with in-order single issue pipeline. Tiny Linux-capable processor for IoT applications.

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

- Low-Power Embedded RISC-V Processor

- Enhanced-Processing Embedded RISC-V Processor

Related News

- MoSys SRAM sports symmetric pipeline

- ChipIdea announces the silicon validation of CI3261Ba, a dual 12-bit 50MS/s pipeline ADC

- ChipIdea announces the silicon validation of CI3350hf, a Dual 8 Bit 105MHz Pipeline ADC

- Feroceon processor reorganizes ARM's pipeline, says In-Stat

Latest News

- Quintauris and Elektrobit Partner to Enable Reliable RISC-V Solutions for Automotive

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3