Processor IP

Filter

Compare

1,834

IP

from

203

vendors

(1

-

10)

-

-

64-bit RISC-V core with in-order single issue pipeline. Tiny Linux-capable processor for IoT applications.

- 64-bit RISC-V core with in-order single issue pipeline based complex.

- Tiny Linux-capable processor optimized for low power and small area.

- Ideally fits IoT applications requiring Linux.

-

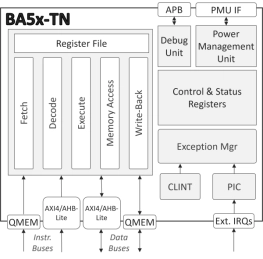

Tiny, Ultra-Low-Power Embedded RISC-V Processor

- The BA5x-TN is a compact, ultra-low power, 32-bit, deeply embedded processor IP core.

- With a two-stage execution pipeline, the processor implements the Embedded variant of the base RV32 ISA (RV32E).

- It uses just 16 general-purpose compressed instructions and omits other resource-demanding extensions.

-

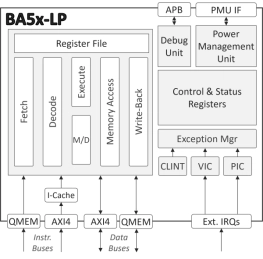

Low-Power Embedded RISC-V Processor

- The BA5x-LP is a highly efficient, low-power, 32-bit, deeply embedded processor IP core.

- The two-stage pipeline processor implements either the RV32I or RV32E instruction set.

- It comes pre-configured with the Multiply/Divide (M) and Compressed Instruction (C) extensions, providing a more flexible and capable platform without a significant increase in area or power.

-

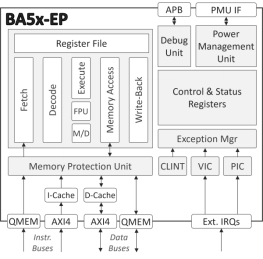

Enhanced-Processing Embedded RISC-V Processor

- The BA5x-EP is a highly-featured 32-bit RISC-V embedded processor IP core optimized for complex, processing-demanding applications.

- It is equipped with a floating-point unit and cache memories, supports hardware-level virtualization, and is suitable for concurrent execution in a multi-processor environment.

-

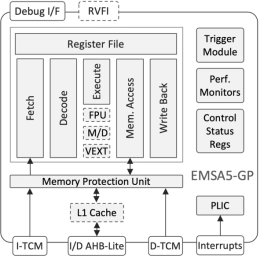

Vector-Capable Embedded RISC-V Processor

- The EMSA5-GP is a highly-featured 32-bit RISC-V embedded processor IP core optimized for processing-demanding applications.

- It is equipped with floating-point and vector-processing units, cache memories, and is suitable for concurrent execution in a multi-processor environment.

-

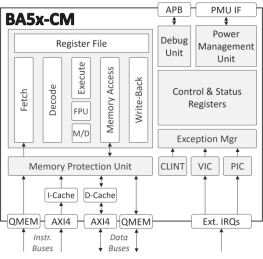

Compact Embedded RISC-V Processor

- The BA5x-CM is a feature-rich 32-bit deeply embedded processor.

- Equipped with a floating-point unit and an instruction cache memory and supporting concurrent execution in a multiprocessor environment, it is well-suited to a wide range of edge IoT and similar applications.

-

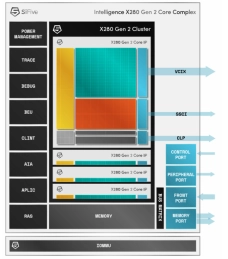

Multi-core capable RISC-V processor with vector extensions

- The SiFive® Intelligence™ X280 Gen 2 is an 8-stage dual issue, in-order, superscalar design with wide vector processing (512 bit VLEN/256-bit DLEN).

- It supports RISC-V Vectors v1.0 (RVV 1.0) and SiFive Intelligence Extensions to accelerate critical AI/ML operations.

-

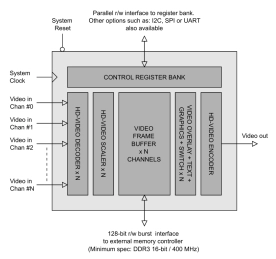

HD Multi-window Video Processor IP Core

- This brief specification describes the operation of the HD Multi-window Video Processor (evaluation) IP Core.

- The IP Core is provided as a netlist in either EDIF, Verilog or VHDL formats.

-

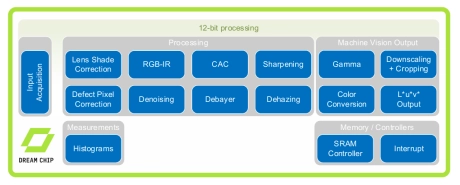

Flexible Pixel Processor Video IP

- The PP300 IP, is a flexible Pixel Processor that provides a wide range of processing functions.

- The PP300 IP offers various system integration options by providing either memory or direct pixel interfaces for input/output pixels.