XpressRICH-AXI IP

Filter

Compare

8

IP

from

1

vendors

(1

-

8)

-

PCIe Controller for USB4 with AXI

- Internal data path size automatically scales up or down (64-, 256-, 512- bits) based on link max. speed and width for reduced gate count and optimal throughput

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs up to Gen4 x8/Gen3 x16 with same RTL code – Gen5 support pending

- Stringent implementation of PCIe to AXI Ordering Rules and AXI to PCIe Ordering Rules guarantees AXI deadlock prevention

- Carefully engineered AXI bridge & AXI interconnect allows full performance on AXI interfaces

-

PCIe Controller for USB4

- Internal data path size automatically scales up or down (256-, 512- bits) based on max. link speed and width for reduced gate count and optimal throughput

- Dynamically adjustable application layer frequency down to 8Mhz for increased power savings

- Optional MSI/MSI-X register remapping to memory for reduced gate count when SR-IOV is implemented

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs (when supported)

- Ultra-low Transmit and Receive latency (excl. PHY)

-

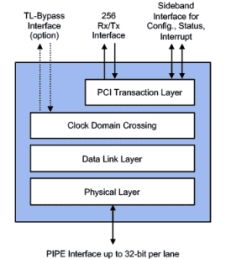

PCIe 3.1 Controller

- Dynamically adjustable application layer frequency down to 8Mhz for increased power savings

- Optional MSI/MSI-X register remapping to memory for reduced gate count when SR-IOV is implemented

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs up to Gen3 x16 with same RTL code

- Ultra-low Transmit and Receive latency (excl. PHY)

- Smart buffer management on receive side (Rx Stream) and transmit side (merged Replay/Transmit buffer) enables lower memory footprint

-

PCIe 2.1 Controller

- Compliant with the PCI Express 2.1/1.1, and PIPE (16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode, Switch port configurations

- Supports x16, x8, x4, x2, x1 at 5 GT/s and 2.5 GT/s speeds

- Supports AER, ECRC, ECC, MSI, MSI-X, Multi-function, crosslink, and other optional features

-

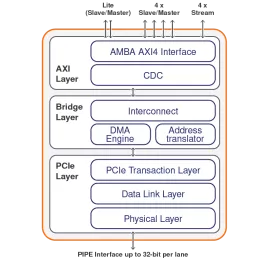

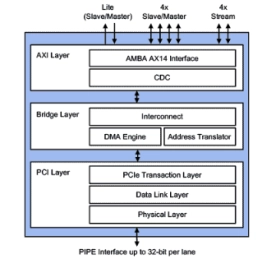

PCIe 2.1 Controller with AXI

- PCIe Interface

- Supported silicon:

- AMBA AXI Interface

- Data Engine and Address translation for PCIe-to-AXI and AXI-to-PCIe transfers

-

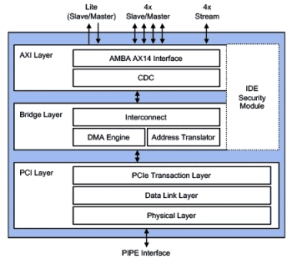

PCIe 4.0 Controller with AXI

- Internal data path size automatically scales up or down (64-, 256- bits) based on link max. speed and width for reduced gate count and optimal throughput

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs up to Gen4 x8/Gen3 x16 with same RTL code

- Stringent implementation of PCIe to AXI Ordering Rules and AXI to PCIe Ordering Rules guarantees AXI deadlock prevention

- Carefully engineered AXI bridge & AXI interconnect allows full performance on AXI interfaces

-

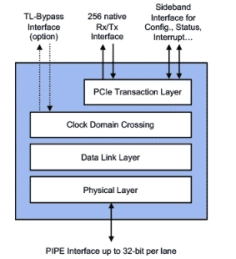

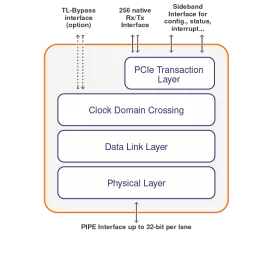

PCIe 4.0 Controller

- Comprises complete PCIe 4.0 interface subsystem with Rambus PCIe 4.0 PHY

- Compliant with the PCI Express 4.0 and 3.1/3.0, and PIPE (8-, 16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode, Switch port configurations

- Supports x16, x8, x4, x2, x1 at 16 GT/s, 8 GT/s, 5 GT/s, 2.5 GT/s speeds

-

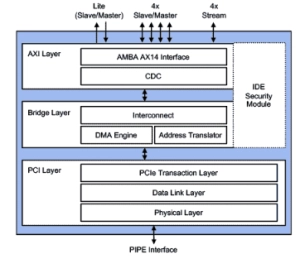

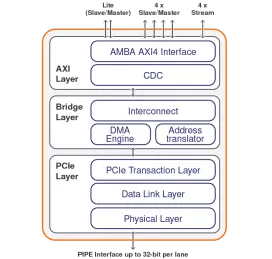

PCIe 3.1 Controller with AXI

- Compliant with the PCI Express 3.1/3.0, and PIPE (16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode configurations

- Supports x16, x8, x4, x2, x1 at 8 GT/s, 5 GT/s, 2.5 GT/s speeds

- Supports AER, ECRC, ECC, MSI, MSI-X, Multi-function, P2P, crosslink, and other optional features

- Supports many ECNs including LTR, L1 PM substates, etc.