XAUI SerDes Phy IP

Filter

Compare

19

IP

from

11

vendors

(1

-

10)

-

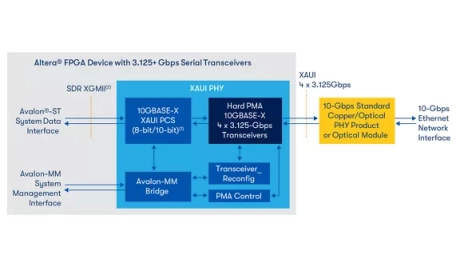

XAUI PHY Intel® FPGA IP

- The XAUI PHY Intel® FPGA IP core allows you to easily build systems with a very high throughput 10G Ethernet connection

- This XAUI PHY along with a 10GbE media access control (MAC) IP core enables an Intel® FPGA to interface to a 10GbE network through a variety of external devices, including a 10GbE PHY device or optical transceiver module.

-

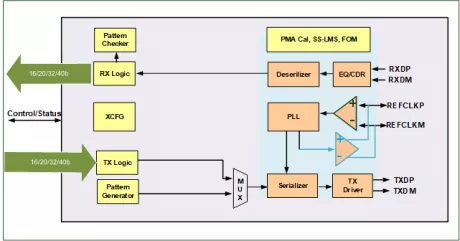

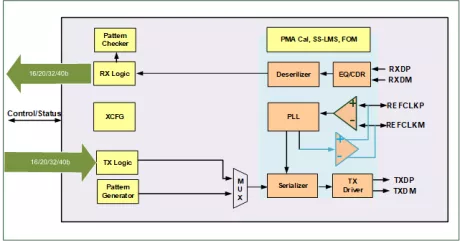

SERDES PHY IP

- Multi-protocol PHYs supporting data rate in the range of 1.25G to 10.3125Gbps

- Support >20dB channel loss

- Flexible ASIC interface for sharing impedance codes among multiple PMA hard macros and reducing the number of external reference resistors for impedance calibration.

- Support RX loss-of-signal detect

-

SerDes PHY IP in TSMC (7nm, 12/16nm, 22nm, 28nm)

- Supports 1.25G to 10.3125Gbps data rates and compact die area

- Supports up to 25dB channel loss@ 5.15625GHz

- Supports RX loss-of-signal detection

- Supports X1, X2 and X4 lanes

-

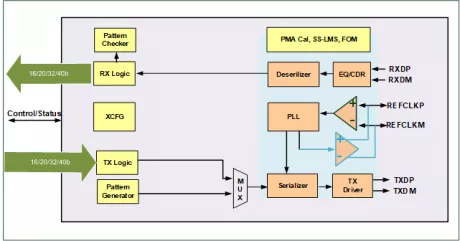

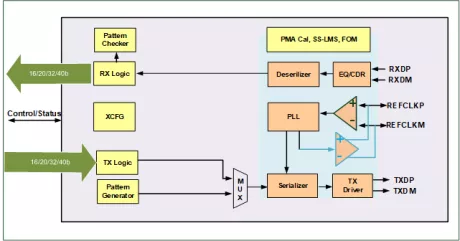

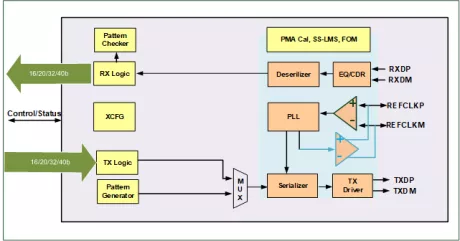

Multi-Standard SerDes PHY

- Configurable parallel data rate of 8 /10 / 16 / 20 / 32 / 40 / 64 / 80

- Input reference 5MHz to support 2.5/5/10G data rates

- Tight control over termination resistor (~50 Ohm) with on chip calibration

- Tight skew control of 1UI between lanes of the PMA

- Multi-tap Tx Finite Impulse Response (FIR) equalizer with multi-level de-emphasis

-

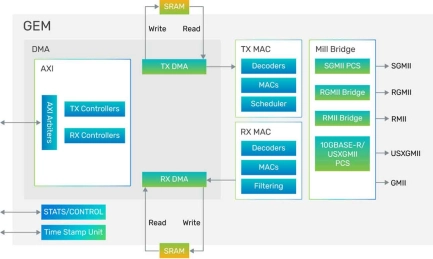

Ethernet PCS IP - Integrates MAC IP to a broad range of PHY and SerDes IP

- Mature: Silicon-proven design in volume production at multiple customers

- Ease-of-use: Customizable with easy integration

- Designed by an Industry Leader: Cadence is an active contributor to the IEEE 802.3 standards working groups

-

5G Combo Serdes for USB/PCIe, TSMC 28HPC+, N/S orientation

- Supports 1.25G to 10.3125Gbps data rates and compact die area

- Supports up to 25dB channel loss@ 5.15625GHz

- Supports RX loss-of-signal detection

- Supports X1, X2 and X4 lanes

-

5G Combo Serdes for USB/PCIe, TSMC 22ULL 2.5V, N/S orientation

- Supports 1.25G to 10.3125Gbps data rates and compact die area

- Supports up to 25dB channel loss@ 5.15625GHz

- Supports RX loss-of-signal detection

- Supports X1, X2 and X4 lanes

-

5G Combo Serdes for USB/PCIe, TSMC 22ULL 1.8V, N/S orientation

- Supports 1.25G to 10.3125Gbps data rates and compact die area

- Supports up to 25dB channel loss@ 5.15625GHz

- Supports RX loss-of-signal detection

- Supports X1, X2 and X4 lanes

-

5G Combo Serdes for USB/PCIe, TSMC 12FFC, N/S orientation

- Supports 1.25G to 10.3125Gbps data rates and compact die area

- Supports up to 25dB channel loss@ 5.15625GHz

- Supports RX loss-of-signal detection

- Supports X1, X2 and X4 lanes

-

10G Combo Serdes for USB/PCIe/Ethernet, SMIC 14FF, N/S orientation

- Supports 1.25G to 10.3125Gbps data rates and compact die area

- Supports up to 25dB channel loss@ 5.15625GHz

- Supports RX loss-of-signal detection

- Supports X1, X2 and X4 lanes