PAM4/NRZ SerDes IP

Filter

Compare

17

IP

from

8

vendors

(1

-

10)

-

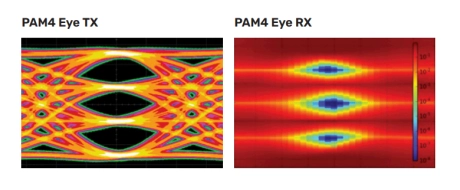

112G-ULR PAM4 SerDes PHY

- Supports full-duplex 1.25Gbps to 112.5Gbps data rates

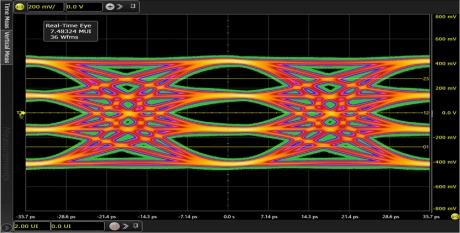

- Superior bit error rate (BER) performance across high-loss and reflective channels

- Compliant with IEEE 802.3ck and OIF standard electrical specifications

- Supports flexible SoC floorplan and IP placement and provides package substrate guideline/reference designs

-

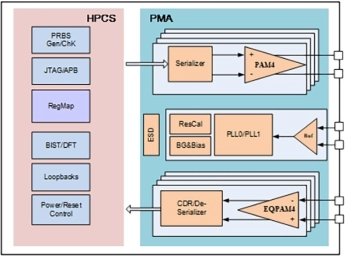

112G-ELR PAM4 SerDes PHY - TSMC 5nm

- TSMC 5nm FinFET CMOS Process

- Power-optimized for ELR and LR links

- Integrated BIST capable of producing and checking PRBS

- 56-112Gbps PAM4 or 1-56Gbps NRZ data rates

-

56G-LR Pam4 SerDes PHY

- Supports Ethernet, FC, CPRI, and eCPRI protocols

- Compliant to IEEE 802.3ck and OIF standard electrical specifications

- Supports 56Gbps PAM4 and 28G, 10G, and sub-10Gbps NRZ data rates

- Unique firmware-controlled adaptive power design provides optimal power and performance tradeoffs and more efficient system designs based on platform requirements

- Continuous calibration and adaption provide robust performance across process, voltage, and temperature

- Supports industrial temperature range -40°C – 125°C

-

64G SerDes

- 4 Channels per Quad, ≤64Gbps; PAM4 support 25~64Gbps; NRZ support 2.5~32Gbps

- Serialization/Deserialization interface width; 64/32/16bits; 64-bit parallel data path in PAM4 mode; 32-bit parallel data path in full-rate NRZ mode; 16-bit and 32-bit parallel data path widths in half-rate and quarter-rate modes

- Four programmable transmitter and receiver configurations selectable by port by using hardware pins or registers. Facilitates fast speed switching during speed negotiation routines

- Aggressive equalization capability to enable 64Gbps operation and legacy system upgrades

-

112G SerDes USR & XSR

- 8 Channels per Macro, 2.5Gbps~112Gbps with TX/RX independent; NRZ Data Rate:2.5-56Gbps PAM4 Data Rates: 56-112Gbps

- Serialization/Deserialization interface width; PCS-User interface support 64bit in PIPE

- Two cascaded PLLs, one LC-tank based and the other ring-oscillator based

- Digitally-control-impedance termination resistors

-

SerDes IP

- 10dB to 35dB bump-to-bump insertion loss

- Multi-rate support for 56Gbps to 112Gbps PAM4 and NRZ

- Integrated PLL

- Robust clock distribution architecture

- Advanced mixed signal analog equalization architecture

- Fully adaptive and programmable RX equalization

- Auto-negotiation

- Link Training

-

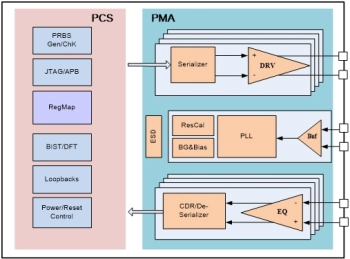

64G High-speed SerDes

- The 64G SerDes PHY is a highly configurable PHY capable of supporting speeds up to 64Gbps within a single lane

- The PHY has been configured to support 64G PAM-4 and NRZ specifically, but the PHY itself can be configured to support a wide range of HS SerDes protocols through changes to the PCS layer and register settings

-

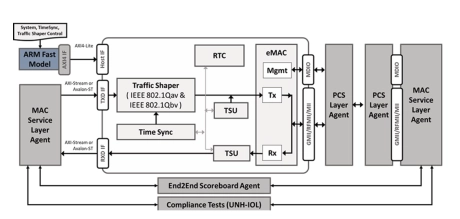

Verification IP for Ethernet

- Avery TSN Ethernet Verification IP provides a complete simulation-based func tional verification solution for core-level and SoC-level verification, including MAC and PHY models, protocol checking, and optional compliance test suite based on UNH-IOL test specifications.

- Additional integration with ARM® Fast Model integration enables running the TSN IP’s software stack in one fully integrated testbench.

-

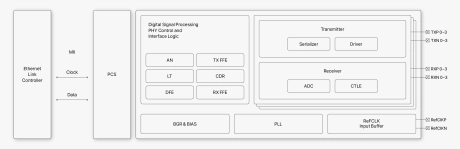

Ethernet PHY IP

- Compliant to 802.3 Ethernet specification - 200GBASE-KR4, 200GBASE-CR4, 100GBASE-KR4, 100GBASE-CR4, 100GBASE-KR2, 100GBASE-CR2, 50GBASE-KR, 50GBASE-CR, 40GBASE-KR4, 40GBASE-CR4, 25GBASE-KR, 25GBASE-CR, 10GBASE-KR, 10GBASE-CR

- Data rate supported - Ethernet: NRZ 3.125 - 26.5625Gb/s, PAM4 53.125Gb/s

- DSP-based architecture using high-performance ADC/DAC for RX/TX

-

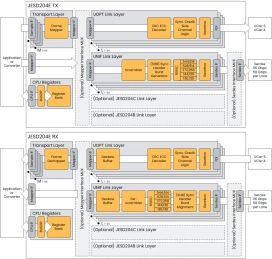

JESD204E Controller IP

- The JESD204E Controller IP from Chip Interfaces is an early adopter’s version of the upcoming revision of the JEDEC standard for Serial Interface for Data Converters.

- The JESD204-E IP core supports the UCIe Optimized Link Layer, a dedicated mode to run JESD over UCIe Modules with Line rates up the 64Gbps per bump, and a JESD204D backwards compatible mode called the Unified Link Layer with line speeds up to 116Gbps with PAM4 and 58Gbps with NRZ and full FEC support.