Arteris IP

Filter

Compare

10

IP

from

1

vendors

(1

-

10)

-

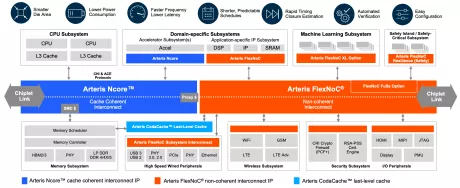

Smart Network-on-Chip (NoC) IP

- Smart NoC automation

- Topology generation with minimum wire length

- Scripting-driven regular topology creation

- Incremental design capability

- Auto-timing closure assist

-

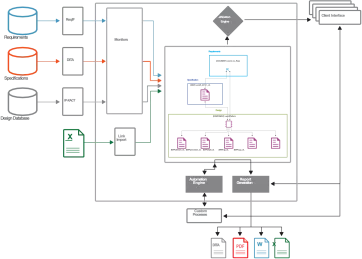

Empowering Design Quality with Harmony Trace

- Comprehensive traceability: Create and maintain traceability between requirements, specifications, hardware designs, software code, tests, and documentation.

- System-of-systems integration: Harmonize disparate systems for end-to-end traceability of all artifacts.

- Tool integration: Link information from leading tools in requirements management, code repository, EDA, software engineering, verification, test, and documentation.

- Multi-domain linking: Enable traceability across multiple domains, providing a comprehensive understanding of the design.

-

HW/SW interface foundation for design innovation

- Various Input Formats:

- CSRSpec Language

- SystemRDL

- IP-XACT

-

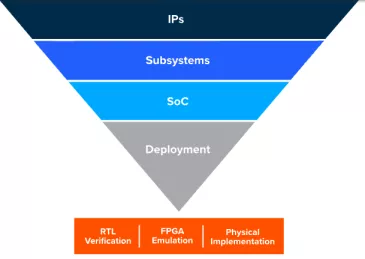

FlexNoC 5 Option For Scalability and Performance Critical Systems

- Scales from 10s to 100s of IP blocks

- Automatically generates ring, mesh and torus networks

- View and edit generated topologies

-

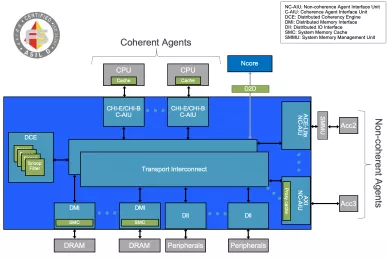

Ncore 3 Coherent Network-on-Chip (NoC)

- Supports multiple coherent agents, including Armv9 and RISC-V CPU clusters

- AMBA CHI-E, CHI-B and ACE interoperability, as well as ACE-Lite and AXI

- Low-latency proxy caches for efficient and quick integration of hardware accelerators into the coherent domain

- Configurable last-level caches

-

Magillem Registers System Integration Automation

- Single database: Import and capture memory map information into a single database (IP-XACT)

- Graphical edition: IP memory map capture & management GUI, system memory map capture & management GUI, system level schematic configurability, GUI with linting cross-checking editor

- Parameterization: including configurable and conditional properties, custom-specific access types, and register modes

- SystemRDL compiler: full support of version 1.0, limited support for version 2.0

-

Magillem Connectivity System Integration Automation

- Project management: Design navigation and data aggregation

- HDL import: Automatic import of structural RTL into a valid IP-XACT design with the support of SystemVerilog, Verilog, and VHDL languages

- IP Packaging: Aggregate component information from different sources in a structured and standard-based format for several design tasks and teams (automatic mapping of bus interfaces, specification of the views with complete fileSet for various skills)

- SoC assembly: Powerful rule-based connectivity, bus interface detection, bus/signal split/tie/open, hierarchical connection, glue logic insertion, feedthrough

-

CodaCache® Last Level Cache IP

- Standalone IP

- 1.2 GHz frequency in 16FF+TT process

- Protocol interoperability: AMBA AXI 4

-

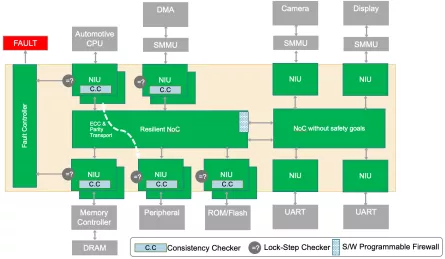

FlexNoC Functional Safety (FuSa) Option helps meet up to ISO 26262 ASIL B and D requirements against random hardware faults.

- ARM® Cortex®-R5 and Cortex-R7 processor port checking

- Hardware duplication and redundancy

- Custom ECC and parity generation and checking

-