RAM IP for TSMC

Welcome to the ultimate

RAM IP

for

TSMC

hub! Explore our vast directory of

RAM IP

for

TSMC

All offers in

RAM IP

for

TSMC

Filter

Compare

18

RAM IP

for

TSMC

from

8

vendors

(1

-

10)

-

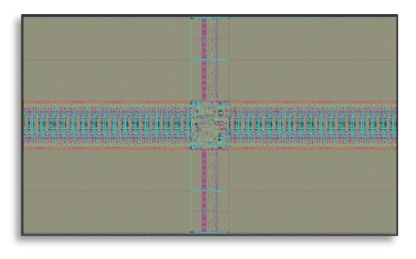

High Speed Single Port Compiler on TSMC 40nm ULP

- Low voltage

- Ultra low power data retention

- Self biasing

- Soft error immunity

-

Memory Compilers

- Dolphin provides a wide range of Memory Compilers and Specialty Memory (ROM, Multi Port RF, CAM, etc.) optimized to meet even the most demanding requirements for high performance, high density and low power.

-

Memory Compiler in TSMC (16nm,22nm,28nm,40nm,55nm,90BCD+,110nm,152nm,180BCD)

- Synchronous read/write operation

- Low leakage current and lower operation power consumption

- Minimum metal layer requirement: 4/3 metal layers

- High density layout structure and small area design

-

High-Density eMRAM Compiler TSMC 22ULL

- eMRAM compiler enabling low-power designs requiring high memory capacity

-

GCRAM, the highest-density on-chip embedded memory in standard CMOS

- High-density bitcell offering up-to 2X area reduction over high-density 6T SRAM.

- Full logic compatibility with standard CMOS, no additional process steps or cost.

-

Single Port SRAM compiler - Memory optimized for ultra high density and low power - compiler range up to 576 k

- Configuration

- SVT transistors for memory periphery

- HD HVT Pushed rule bit cell from foundry

- Smart periphery design

-

Single Port SRAM compiler - Memory optimized for high density and low power - compiler range up to 320 k

- Foundry sponsored memory generator

- Configuration

- uLL TSMC Bit-cell for memory core and uLL MOS for memory periphery

- Migration of an existing architecture already available for other processes (90, 85, 55 nm)

-

Single Port SRAM compiler - Memory optimized for ultra high density and high speed - compiler range up to 320 k

- Configuration

- SVT MOS for memory periphery

- uHD HVT pushed rule bit-cell from foundry

- Smart periphery design to reach the highest density

-

Single Port SRAM compiler - Memory optimized for high density and low power - compiler range up to 320 k

- ConfigurationSVT/HVT MOS for memory peripheryuHD HVT pushed rule bit-cell from foundry Designed with 4 metal layers, routing enabled over the memory in metal 4 within free routing tracksMigration on an existing architecture already available for other processes (90, 85, 55 nm)Smart periphery design to reach the highest densityUp to 20% denser than standard memory generators at 55 nmUltra low leakage designData retention mode at nominal voltage (1.2 V) and low voltage (0.7 V): for 4x leakage reductionLow dynamic powerPartitioned arrayVariable write-mask capability Easy integrationMUX optionsData range flexibility allows easy addition of bits for redundancy or ECC purposesAddress range flexibility allows easy addition of single rows for redundancy purposes The Dolphin qualityComplete mismatch validation of the memory architecture taking in account local and global dispersionOptional BIST for industrial fabrication test of instances

-

Single Port SRAM compiler - Memory optimized for high density and low power - compiler range up to 320 k

- Migration of an existing architecture already available for other processes (90, 85, 55 nm)

- Smart periphery design to reach the highest density

- Memory designed with SVT MOS for periphery and SVT uHD PRBC from TSMC for memory core

- Ultra Low dynamic power