PCI Express IP for SMIC

Welcome to the ultimate

PCI Express IP

for

SMIC

hub! Explore our vast directory of

PCI Express IP

for

SMIC

All offers in

PCI Express IP

for

SMIC

Filter

Compare

10

PCI Express IP

for

SMIC

from

5

vendors

(1

-

10)

-

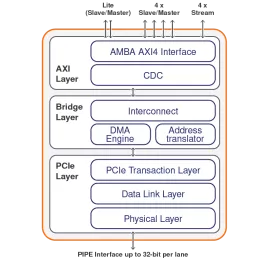

PCIe 3.1 Controller with AXI

- Compliant with the PCI Express 3.1/3.0, and PIPE (16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode configurations

- Supports x16, x8, x4, x2, x1 at 8 GT/s, 5 GT/s, 2.5 GT/s speeds

- Supports AER, ECRC, ECC, MSI, MSI-X, Multi-function, P2P, crosslink, and other optional features

- Supports many ECNs including LTR, L1 PM substates, etc.

-

PCIe 2.0 PHY, SMIC 28HKMG18 x1, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

USB 2.0 PHY

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version 1.0

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- USB Data Recovery and Clock Recovery on receiving

- SYNC and EOP generation on transmit packets and detection on receive packets

-

PCIe PHY

- Support for PCIe3(8.0Gbps),Backward compatible with 2.5Gbps and 5Gbps for PCIe

- Full compatible with PIPE4.2 interface specification

- Support 16bit and 32bit parallel data bus

- Independent channel power down control

- Supported reference clock input range from 25M to 400M

-

CXL Controller

- Compliant with CXL Specification version 2.0/1.1 and PCIe Base Specification 5.0 (32 Gbps per lane)

- Complaint with PIPE 5.x interface

- Supports X16, X8, X4, X2 and X1 lane widths

- Supports 512, 256 and 128 Data path widths

- Supports PCI Express Alternate Protocol

-

PCIe Controller

- Compliant to PCI Express base specification 5.0 (32 Gbps per lane) and backward compatible with PCI Express versions 4.0, 3.1, 2.0 and 1.1

- Supports configurable number of PFs and VFs for SR-IOV

- Architected for high link utilization and low latency

- Efficient receive and transmit-retry buffering scheme

-

PCIe 2.1 PHY(12nm,14nm, 16nm, 28nm, 40nm, 55nm)

- Fully compliant with PCI Express Base 2.1 and PCI Express Base 1.1 electrical specifications

- Compliant with PIPE4.4.1 (PCIe) specification

- Supports all power saving modes (P0, P0s, P1, P2) defined in PIPE4.4.1 specification

- Supports L1 PM Substates with CLKREQ#

-

PCIe 3.1 PHY (6nm, 7nm, 12nm, 14nm, 16nm, 22nm, 28nm and 40nm)

- Compliant with PC1 Express 3.0 (8.0 GT/s), 2.1 (5.OGT/s) and 1 .I (2.5GT/s) as well as the PIPE 4.0 specifications

- Supports the power saving modes L0, L0s, L1 and L2

-

PCIe Gen2 PHY

- ? 5-Gbps data transmission rate

- ? PIPE3-compliant transceiver interface, configurable using soft Physical Coding Sublayer (PCS)

- layer above hard macro PHY

- ? Supports 8-bit interface at 500-MHz operation

-

PCIe 2.0 PHY in SMIC (40nm, 28nm)

- Physical coding sublayer (PCS) block with PIPE interface

- Supports PCIe power management features, including L1 substate

- Power gating for lowest standby power

- Low active power using voltage mode TX with under drive supply options