Other

All offers in

Other

Filter

Compare

26

Other

from

16

vendors

(1

-

10)

-

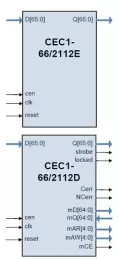

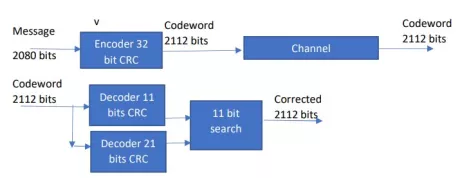

66/2112 Codec for Cyclic Code (2112,2080)

- Small Size

- Implements FEC Sublayer for 10GBASE-R (section 74 of the IEEE 802.3 standard)

- 10G/40G/100G Ethernet MAC-friendly interface

- Practically self-contained: requires only memory for one 2112-bit block in the decoder.

-

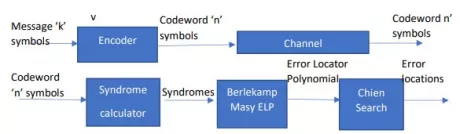

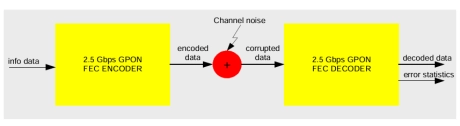

2.5 Gbps GPON FEC Codec

- This high performance core is a full featured Forward Error Correction encoder and decoder, specially designed for high speed optical networks or any other broadband applications.

- It is fully compliant with the 2.5 Gbps GPON standard (G.984.3) and is available for FPGA or ASIC implementation.

- The FEC algorithm is based on Reed-Solomon (255,239) code and consists of an encoder and decoder module.

-

oFEC Encoder and Decoder

- OpenROADM oFEC (Open Forward Error Correction) is a core element of the OpenROADM initiative, providing a standardized, open-source FEC solution for high-speed coherent optical networks.

- The oFEC IP cores deliver high coding gain through a fully parallel, pipelined decoder architecture with 3 soft-decision (SD) and 2 hard-decision (HD) decoding steps. It supports data rates from 200G to 800G, including Probabilistic Constellation Shaping (PCS) modes to enhance spectral efficiency, noise tolerance, and transmission reach.

-

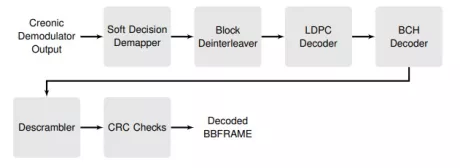

DVB-S2X LDPC/BCH Decoder

- Compliant with DVB-S2 and DVB-S2X

- Support for decoding of BBFRAMEs

- Support for ACM, CCM, and VCM

- Support for very low SNR modes (VLSNR) with SNRs below -9 dB

-

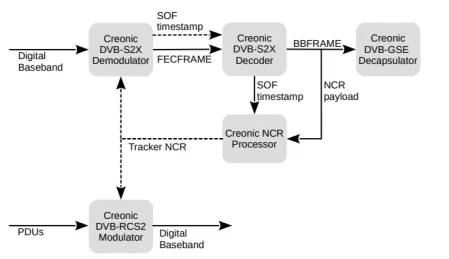

NCR Processor

- NCR (Network Clock Reference) is a procedure to provide the master clock (i.e. time information) of the satellite to all its user terminals.

- Typically, NCR packets are provided periodically over a continuous DVB-S2 or DVB-S2X link.

- The receiving user terminal uses the knowledge of the master clock in the system to determine when it is allowed to transmit data in a time-division multiple access (TDMA) system, such as DVB-RCS or DVB-RCS2.

-

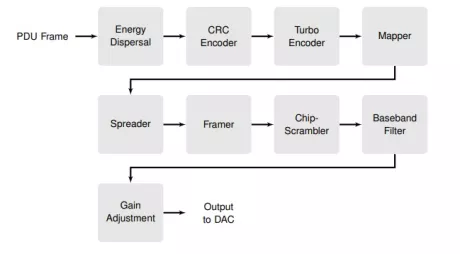

DVB-RCS2 Modulator

- Compliant with DVB-RCS2

- Support for Pi/2-BPSK, QPSK, 8-PSK, and 16-QAM

- Support for all linear burst modulation waveforms specified in Annex A

- Output baseband-filtered and gain adjusted samples

-

BCH Encoder/Decoder IP Core

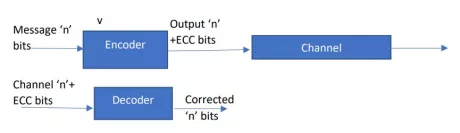

- Full hardware implementationfor maximum performance, encoding, errordetectionand correct

- Balanced performance/gatecount

- All Galois fields covered

- ValidatedIP reducesTime-To-Market

-

-

FireCode FEC

- Encoding and decoding is performed in 0 clock cycles.

- No iterative Feedback in the pipeline

- No RAMS/ROMS used.

-

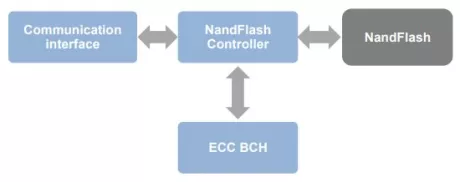

BCH Error Correcting Code ECC

- Asynchronous operation

- No clocks required.

- No storage like memories SRAMS/ROMS/FilipFlops used

- No iterative Feedback in the pipeline