IP for TSMC

Welcome to the ultimate

IP

for

TSMC

hub! Explore our vast directory of

IP

for

TSMC

All offers in

IP

for

TSMC

Filter

Compare

460

IP

for

TSMC

from

29

vendors

(1

-

10)

Filter:

- 16nm

-

-

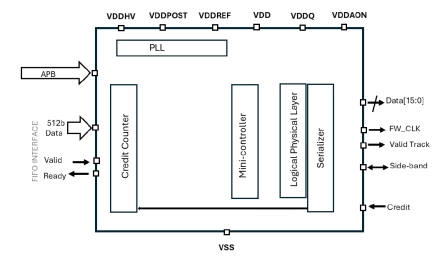

UCIe TX Interface

- Transmit-only UCIe REV1.1 with FIFO Interface

- TSMC 16FFC process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

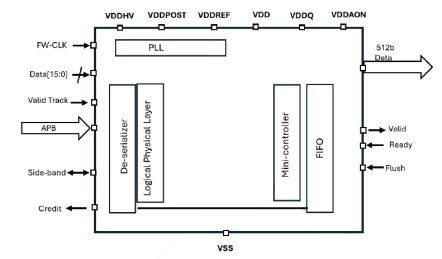

UCIe RX Interface

- Receive-only UCIe Rev1.1 with FIFO Interface

- Samsung 8nm process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

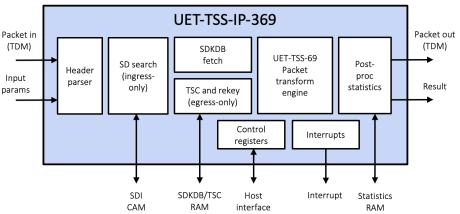

Multi-channel Ultra Ethernet TSS Complete Layer

- The UET-TSS-IP-369 (EIP-369) is an inline, high-performance, multi-channel packet engine that provides the complete TSS layer, bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

- The EIP-369 embeds the UET-TSS-IP-69 for the packet transformation.

-

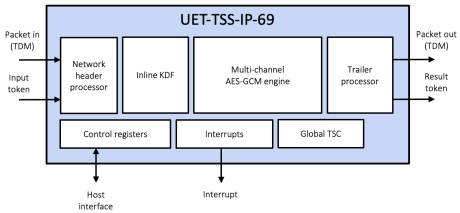

Multi-channel Ultra Ethernet TSS Transform Engine

- The UET-TSS-IP-69 (EIP-69) is a high-performance, multi-channel transform engine that provides the complete TSS packet transformation (including KDF and IP/UDP updates), bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

-

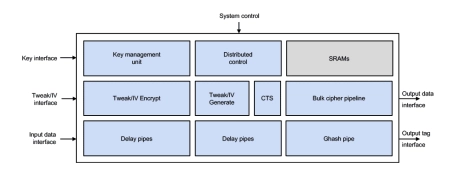

Fast Inline Cipher Engine, AES-XTS/GCM, SM4-XTS/GCM, DPA

- One input word per clock without any backpressure

- Design can switch stream, algorithm, mode, key and/or direction every clock cycle

- GCM: throughput is solely determined by the data width, data alignment and clock frequency

- XTS: block processing rate may be limited by the number of configured tweak encryption & CTS cores; a configuration allowing 1 block/clock is available

-

10-bit 2.5GSPS ADC

- The ODT-ADS-10B2P5G-T16 is an ultra lowpower, high-performance time-interleaved ADC designed in a 16nm CMOS process.

- This 10-bit, 2.5GSPS ADC supports input signals up to 1.0 GHz and features a differential full-scale range of 1.0Vpp with excellent static and dynamic performance.

-

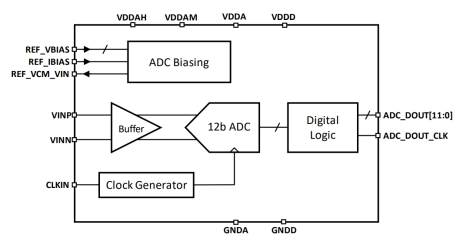

12 bit, 200 MSPS ADC on TSMC 16nm FFC

- The ODT-ADS-12B200M-16FFCT is an ultra low power ADC designed in a 16nm CMOS process.

- This 12-bit, 200MSPS ADC supports input signals up to 100MHz and features a differential full-scale range of 1.0Vpp and excellent static and dynamic performance.

-

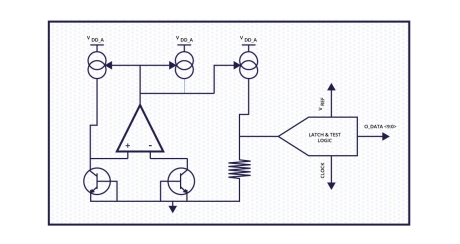

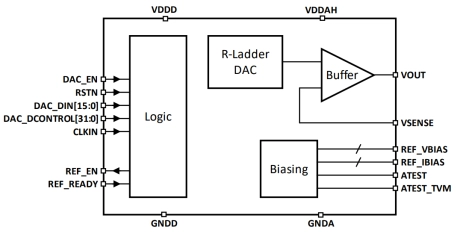

16-bit 5MSPS DAC on TSMC 16 FFC

- The ODT-DAC-16B5M-SV-T16 is an ultra-low power, voltage output, 16-bit DAC with a high performance, class AB output buffer.

- The DAC uses a proprietary architecture that guarantees monotonicity. It also features low glitch, low drift, small area and low power consumption.

- VSENSE pin is provided to set the load voltage with high accuracy. Both VOUT and VSENSE pins must be routed to the load.

-

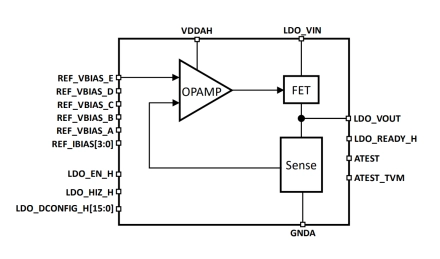

External Compensated LDO - 300mA Output on TSMC 16 FFC

- The ODT-LDO-EC-300M-16FFCT is a low dropout (LDO), linear regulator for integration in a SoC.

- The LDO uses advanced control techniques to achieve excellent transient response, excellent PSRR performance and low noise.

- The LDO has an integrated pass transistor and is stable with an off-chip capacitor of 10µF.