10-bit 2.5GSPS ADC

The ODT-ADS-10B2P5G-T16 is an ultra lowpower, high-performance time-interleaved ADC designed in a 16nm CMOS process.

Overview

The ODT-ADS-10B2P5G-T16 is an ultra lowpower, high-performance time-interleaved ADC designed in a 16nm CMOS process.

This 10-bit, 2.5GSPS ADC supports input signals up to 1.0 GHz and features a differential full-scale range of 1.0Vpp with excellent static and dynamic performance.

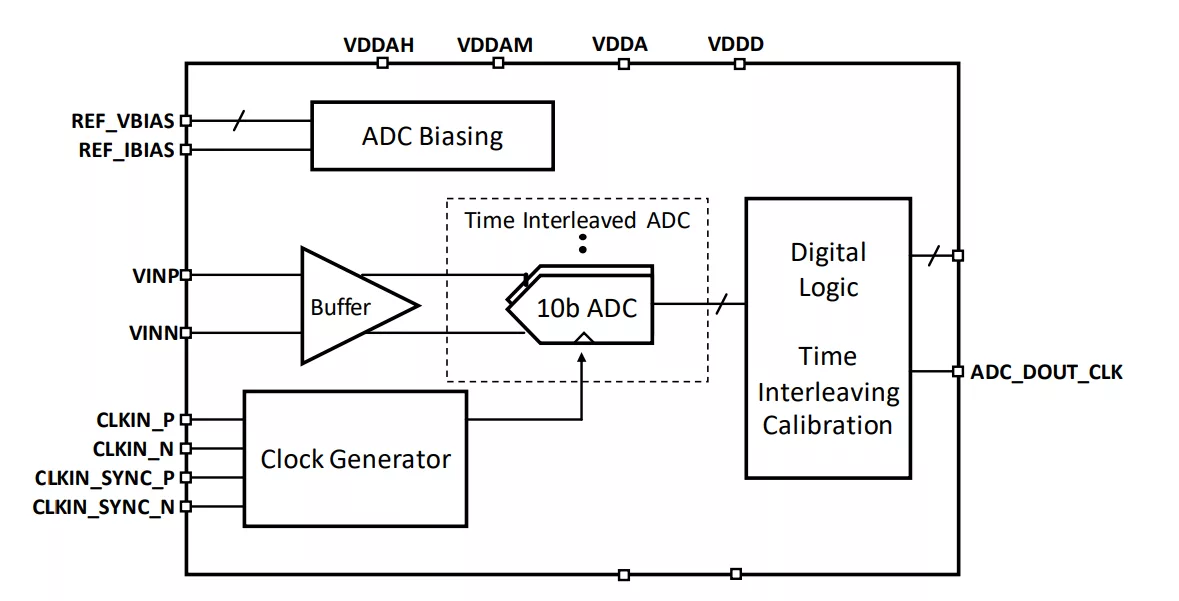

The ADC architecture is optimized to maximize performance while minimizing power and area consumption. The ADC input is buffered by an optional input buffer and then distributed to timeinterleaved ADC channels. The ADC includes built in calibration to remove time interleaving artifacts, including offset mismatch, gain mismatch and timing skew.

To maximize SNR, the ADC includes an ultra-lowjitter clock distribution network with aperture jitter of 150fsrms.

Key features

- TSMC 16/12nm FFC

- Ultra low-power, high-performance ADC

- 10-bit ADC resolution

- Sampling rate up to 2.5GSPS

- Fully differential operation

- 1.0Vpp differential input signal range

- In-band SFDR of 57dBc

- SNDR up to 50dB

- Internal calibration circuitry to correct timeinterleaving errors

- Power dissipation scalable with sampling rate

Block Diagram

Benefits

- High Performance Low Power, Low Area

Applications

- General purpose software defined radio

- High speed data acquisition systems

- Cellular base station

- Broadband communications

- High-speed medical imaging

- Wideband satellite receiver

What’s Included?

- Datasheet

- Hard Macro (GDSII)

- Characterization Report (as applicable)

- Abstract View (LEF) for top level connectivity

- Spectre Netlist (as needed upon request)

- Behavioral Model

- Integration and Customer Support

Specifications

Identity

Analog

Provider

Learn more about ADC IP core

Time Interleaving of Analog to Digital Converters: Calibration Techniques, Limitations & what to look in Time Interleaved ADC IP prior to licensing

Three ways of looking at a sigma-delta ADC device

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Save power in IoT SoCs by leveraging ADC characteristics

High Speed ADC Data Transfer

Frequently asked questions about ADC IP cores

What is 10-bit 2.5GSPS ADC?

10-bit 2.5GSPS ADC is a ADC IP core from Omni Design Technologies, Inc. listed on Semi IP Hub.

How should engineers evaluate this ADC?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this ADC IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.