Security IP for TSMC

Welcome to the ultimate

Security IP

for

TSMC

hub! Explore our vast directory of

Security IP

for

TSMC

All offers in

Security IP

for

TSMC

Filter

Compare

31

Security IP

for

TSMC

from

2

vendors

(1

-

10)

Filter:

- 16nm

-

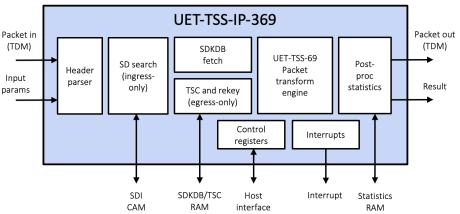

Multi-channel Ultra Ethernet TSS Complete Layer

- The UET-TSS-IP-369 (EIP-369) is an inline, high-performance, multi-channel packet engine that provides the complete TSS layer, bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

- The EIP-369 embeds the UET-TSS-IP-69 for the packet transformation.

-

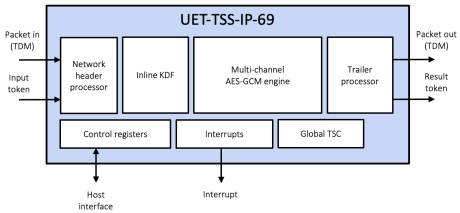

Multi-channel Ultra Ethernet TSS Transform Engine

- The UET-TSS-IP-69 (EIP-69) is a high-performance, multi-channel transform engine that provides the complete TSS packet transformation (including KDF and IP/UDP updates), bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

-

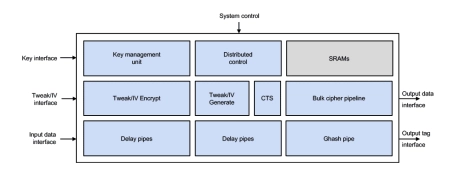

Fast Inline Cipher Engine, AES-XTS/GCM, SM4-XTS/GCM, DPA

- One input word per clock without any backpressure

- Design can switch stream, algorithm, mode, key and/or direction every clock cycle

- GCM: throughput is solely determined by the data width, data alignment and clock frequency

- XTS: block processing rate may be limited by the number of configured tweak encryption & CTS cores; a configuration allowing 1 block/clock is available

-

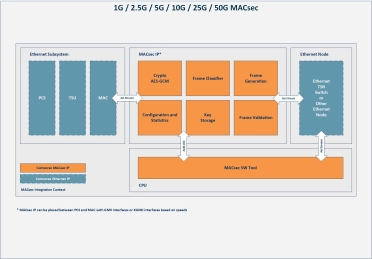

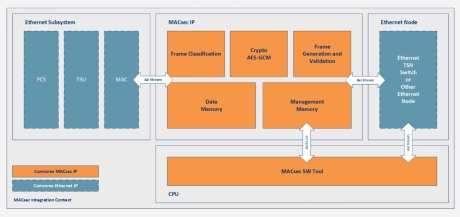

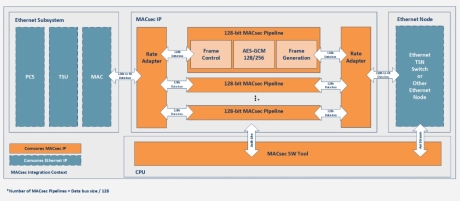

1G/2.5G/5G/10G/25G/50G MACsec

- The MACsec IP provides Ethernet Layer 2 Security for port authentication, data confidentiality and data integrity as standardized in IEEE 802.1AE.

- It protects components in Ethernet networks especially high-speed Ethernet used in automotive, industrial, cloud, data center, and wireless infrastructure.

- The MACsec IP is a fully compliant solution that provides line-rate encryption and supports VLAN-in-Clear.

-

10M MACsec

- The MACsec IP provides Ethernet Layer 2 Security for port authentication, data confidentiality and data integrity as standardized in IEEE 802.1AE.

- It protects components in Ethernet networks especially very low-speed Ethernet used in automotive, industrial, and consumer applications.

- The MACsec IP is a fully compliant solution that provides line-rate encryption and is optimized for the smallest area size.

-

100G / 200G / 400G / 800G / 1.6T MACsec

- The MACsec IP provides Ethernet Layer 2 Security for port authentication, data confidentiality and data integrity as standardized in IEEE 802.1AE.

- It protects components in Ethernet networks especially very high-speed Ethernet used in cloud, data center, and backhaul networks.

- The MACsec IP is a fully compliant solution that provides line-rate encryption and supports VLAN-in-Clear.

-

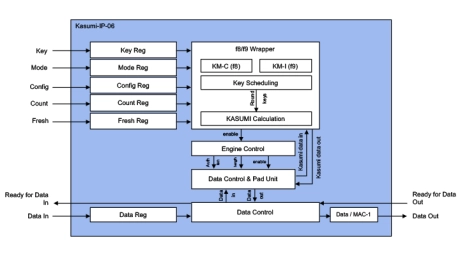

3GPP Kasumi Accelerators

- Wide bus interface (64-bit data, 128-bit keys) or 32-bit register interface.

- Includes key scheduling hardware.

- Modes Kasumi

- Algorithms f8 and f9.

- Fully synchronous design.

- Low Speed, High Speed versions.

-

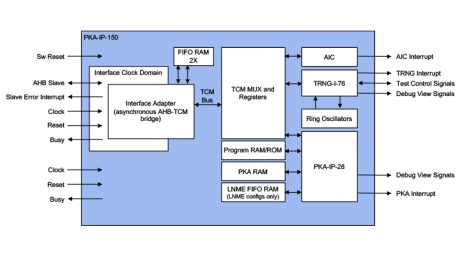

RSA/ECC Public Key Accelerators with TRNG and AHB

- Up to 4160-bit modulus size for RSA & 768-bit modulus for prime field ECC operations

- Public key signature generation, verification and key negotiation with little involvement of host

- NIST CAVP compliant for FIPS 140-3

-

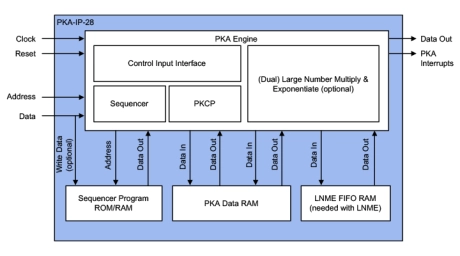

Small RSA/ECC Public Key Accelerators

- The PKA-IP-28 is a family of Public Key Accelerator IP cores designed for full scalability and an optimal “performance over gate count” deployment.

- Proven in silicon, the PKA-IP-28 public key accelerator addresses the unique needs of semiconductor OEMs and provides a reliable and cost-effective solution that is easy to integrate into SoC designs.

-

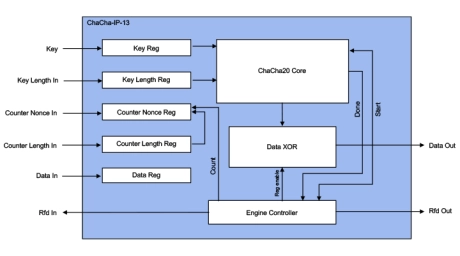

ChaCha20 Accelerators

- The ChaCha-IP-13 (EIP-13) is an IP solution for accelerating the ChaCha20 cipher algorithm (RFC7539), supporting the NIST CTR mode up to 12.8 Gbps @ 300MHz.

- Designed for fast integration, low gate count and full transforms, the ChaCha-IP-13 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high-speed crypto pipelines.