IP for TSMC

Welcome to the ultimate

IP

for

TSMC

hub! Explore our vast directory of

IP

for

TSMC

All offers in

IP

for

TSMC

Filter

Compare

3,903

IP

for

TSMC

from

105

vendors

(1

-

10)

-

-

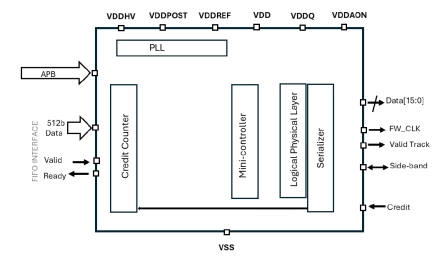

UCIe TX Interface

- Transmit-only UCIe REV1.1 with FIFO Interface

- TSMC 16FFC process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

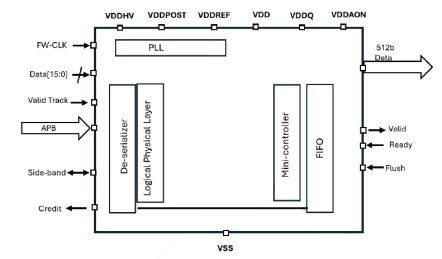

UCIe RX Interface

- Receive-only UCIe Rev1.1 with FIFO Interface

- Samsung 8nm process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

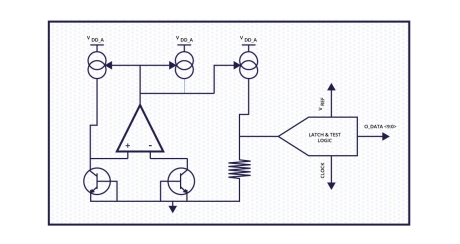

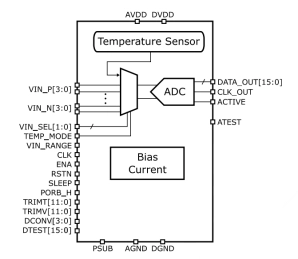

Ultra-Low-Power Temperature/Voltage Monitor

- ± 4C temperature accuracy without trim

- ± 1C temperature accuracy after single room temperature trim

- 0.011C temperature resolution

- Voltage monitor supports both single-ended and differential inputs, with 4:1 input mux

-

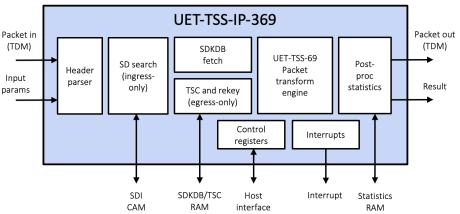

Multi-channel Ultra Ethernet TSS Complete Layer

- The UET-TSS-IP-369 (EIP-369) is an inline, high-performance, multi-channel packet engine that provides the complete TSS layer, bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

- The EIP-369 embeds the UET-TSS-IP-69 for the packet transformation.

-

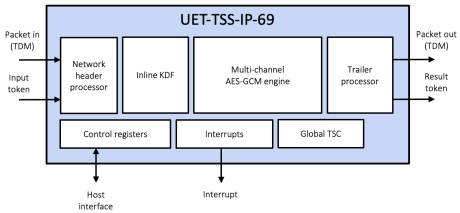

Multi-channel Ultra Ethernet TSS Transform Engine

- The UET-TSS-IP-69 (EIP-69) is a high-performance, multi-channel transform engine that provides the complete TSS packet transformation (including KDF and IP/UDP updates), bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

-

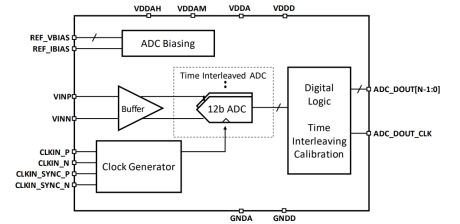

Ultra high-performance low-power ADC

- TSMC 28nm

- Ultra high-performance low-power ADC

- 12-bit ADC resolution

- Sampling rate up to 5GSPS

-

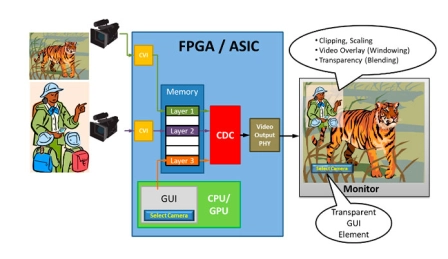

Customizable Display Controller IP

- CDC is a fully Customizable Display Controller IP supporting up to 16k resolutions (4096x4096 pixel) on a MIPI-DPI compliant parallel video output.

- Several features can be configured at synthesis time and programmed at run time.

- The display controller can be applied to e.g. FPGA systems with a resource optimized, application specific feature configuration or to ASIC projects applying a more generic feature set and thus more flexibility.

-

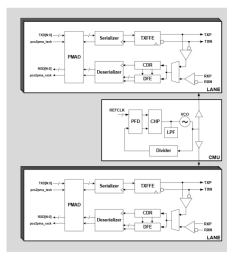

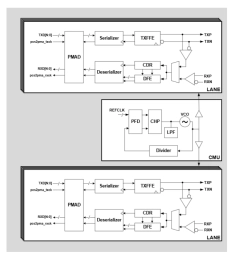

Ultra-Low Latency 32Gbps SerDes IP in TSMC 12nm FFC

- Modular architecture supporting x1 to x16 lanes with a single CMU

- Lane-based PLL architecture supporting flexible, independent data rates from 1.25 to 32Gbps

- Ultra-low latency 2/4/8-bit parallel interface mode for lowest possible latency

-

Ultra-Low Latency 32Gbps SerDes IP in TSMC 22nm ULP

- Modular architecture supporting x1 to x16 lanes with a single CMU

- Lane-based PLL architecture supporting flexible, independent data rates from 1.25 to 32Gbps

- Ultra-low latency 2/4/8-bit parallel interface mode for lowest possible latency