Embedded Memories IP for TSMC

Welcome to the ultimate

Embedded Memories IP

for

TSMC

hub! Explore our vast directory of

Embedded Memories IP

for

TSMC

All offers in

Embedded Memories IP

for

TSMC

Filter

Compare

64

Embedded Memories IP

for

TSMC

from

13

vendors

(1

-

10)

-

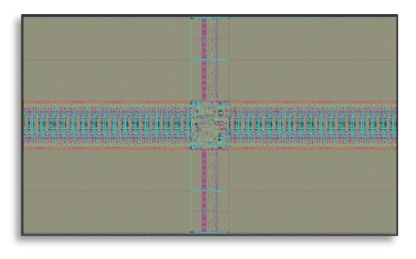

High Speed Single Port Compiler on TSMC 40nm ULP

- Low voltage

- Ultra low power data retention

- Self biasing

- Soft error immunity

-

Embedded flash IP, 1.8V/5V TSMC 180nmBCD

- Supports high temperature and long retention life time for severe automotive requirement

- Low power in Program/Erase operation for power critical applications

- Requires few (2~3) additional masks

- No change to SPICE model of Standard CMOS process, for re-using existing design and IP

-

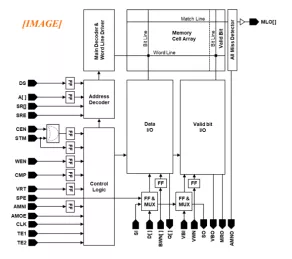

eTCAM (Embedded Ternary Content Addressable Memory IP

- One cycle operation latency (without priority encoder)

- Valid Bit per entry to reduce power

- Valid Bit reset in one cycle support

- Mask input option for bit-write and masked search key

-

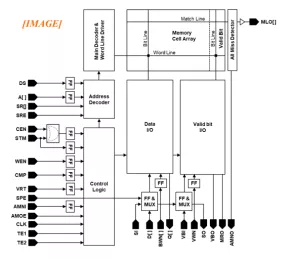

eTCAM (Embedded Ternary Content Addressable Memory IP

- One cycle operation latency (without priority encoder)

- Valid Bit per entry to reduce power

- Valid Bit reset in one cycle support

-

sROMet compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 1M

- Foundry sponsored - sROMet compiler - TSMC 55 nm uLPeFlash - Non volatile memory optimized for high density and low power - Dual Voltage - compiler range up to 1M

-

sROMet compiler - Memory optimized for high density and low power - Dual Voltage - compiler range up to 1M

- REDUCE DIE COST

- Via 1 programmable ROM

- Key patent for high density with a single programming layer

- Gain in density over alternative ROM designs

-

Memory Compilers

- Dolphin provides a wide range of Memory Compilers and Specialty Memory (ROM, Multi Port RF, CAM, etc.) optimized to meet even the most demanding requirements for high performance, high density and low power.

-

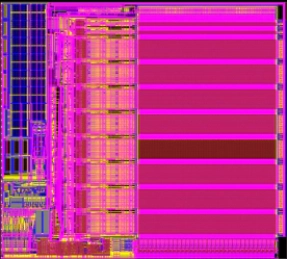

Memory Compiler in TSMC (16nm,22nm,28nm,40nm,55nm,90BCD+,110nm,152nm,180BCD)

- Synchronous read/write operation

- Low leakage current and lower operation power consumption

- Minimum metal layer requirement: 4/3 metal layers

- High density layout structure and small area design

-

TSMC CLN16FFC Ultra High Density One Port Register File

- The Ultra High Density One Port Register File operates within voltage range from 0.72 V to 0.88 V and junction temperature range from -40 °C to 125 °C. The available supported macro size is configurable from 128 bits to 72K bits. The Compiler is divided into 3 groups according to their column selection numbers (Mux=1, 2 or 4).

- Pins and metal layers

- 1P4M (2Xa1Xd_h): 4 metal layers used and top metal is MXd.

- Power mesh supported with M4 pins

-

Embedded Flash IP,64Kx8 bits for 1.8V/5V/32V HV

- Logic Embedded IP

- Programming with channel hot electron injection, erasing with FN erase

- High yield performance

- Small IP size