sureCore Delivers 40nmULP Memory Compiler

sureCore Delivers 40nmULP Memory Compiler

Opens up new power-critical possibilities for IoT applications

Sheffield, England - June 3, 2016 - sureCore Ltd., the low power SRAM IP leader, today announced the immediate availability of its TSMC 40nmULP process technology memory compiler.

The new compiler facilitates utilisation of sureCore's recently announced 40nm Ultra Low Voltage SRAM IP that effectively operates at a record-setting 0.6V across process voltage and temperature.

The new 40nm ULP compiler supports synchronous single port SRAM with operating voltages ranging from 0.6 to 1.21 volts and memory capacities ranging from 8Kbytes to 576Kbytes with maximum word lengths of 72bits.

Previous test chip results revealed an up to 80% savings in dynamic power consumption and up to 75% reduction in static power.

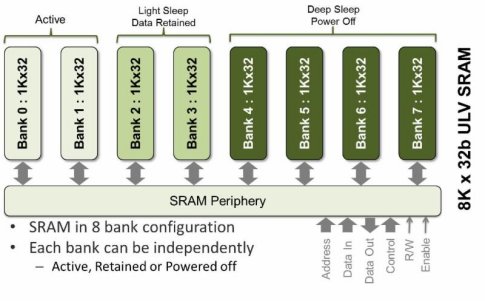

The design targets power-critical "keep alive" IoT, wearable and medical applications. The SRAM itself is single rail and DVFS compatible. A rich suite of power management options include light sleep, deep sleep and power-down modes. The array is subdivided into up to eight banks that can be in independently active, retained or powered off modes. The compiler also provides Design-for-Test (DFT) and BIST support.

The sureCore low power SRAM IP is proving critical for a variety of IoT, wearable and medical applications that mandate keep alive memory. It enables automated spoken word or phrase recognition and over or under temperature events.

sureCore's Ultra Low power SRAM enables computing at formerly unattainable low voltages levels of 0.6V. By combining low voltage operation with the leakage characteristics of the underlying process, sureCore has created an SRAM that supports operating speeds down to 20MHz at 0.6V and exceeds 300MHz at 1.1V.

"The 40nm ultra-low power process technology is, arguably, the cost effective sweet spot for many IoT, wearable and medical applications where long battery life is must," said Paul Wells, sureCore's CEO. "Mature nodes such as 40nm represent a sweet spot for IoT technical and business challenges and the sureCore Ultra Low power SRAM is quickly being acknowledged the leading power critical solution."

The company also has a 28nm FDSOI compiler and is currently working on a 22nm FDSOI Compiler, according to d'Eyssautier, who identified the technology as another popular IoT node.

|

|

| sureCore's new 40nm ULP SRAM IP opens up new power-critical possibilities for IoT applications. It is subdivided into up to eight system-friendly sleep modes that can be in independently active, retained or powered off modes. |

About sureCore www.sure-core.com

sureCore Limited is an SRAM IP company based in Sheffield, UK, developing low power memories for current and next generation, silicon process technologies. Its award-winning, world-leading, low power SRAM design is process independent and variability tolerant, making it suitable for a wide range of technology nodes. This IP will help SoC developers meet both challenging power budgets and manufacturability constraints posed by leading edge process nodes.

Related Semiconductor IP

Related News

- sureCore announces low power memory compiler for 16nm FinFET

- sureCore Delivers FDSOI 28nm Memory Compiler

- sureCore Opens Low Power Memory Compiler Access

- sureCore announces range of off-the-shelf, ultra-low power memory IP to help fast-track power critical designs

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud