DFSPI IP Core from DCD supports all serial memories available on the market.

Bytom, Poland -- June 16, 2023 -- Digital Core Design, the leading IP Core provider and System-on-Chip design house, presents its latest DFSPI IP Core for access to NOR and NAND Flash Devices. And if universal NOR & NAND Flash IP is not enough… DCD’s DFSPI IP Core supports also MRAM, pSRAM, DRAM, and EEPROM - combining the ease of use with the reliability, low power, and speed under all conditions, including automotive, industrial, and other applications.

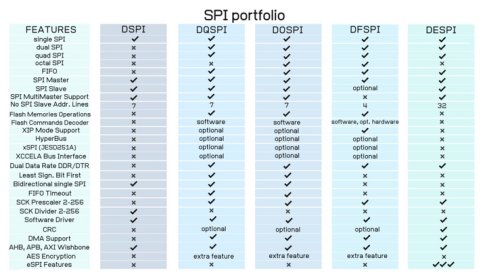

DFSPI IP Core is a real “combo” between all SPI IP Cores available on the market – it’s an SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL, QUAD, OCTAL SPI Bus Controller with DDR / DTR support and optional AES Encryption) + NOR & NAND Flash Memory Support for all serial memories available on the market.

- As an option, the DFSPI controller has a built-in support for HyperBusTM specification and xSPI (Expanded Serial Peripheral Interface – JESD251A) specification – explains Jacek Hanke, DCD CEO The same the SPI Controller allows easy communication with all available SPI FLASH memories.

The DFSP IP Core is compatible with the xSPI JESD251 standard, which can be accessed through a standard AXI4 slave interface. It offers backward compatibility with Octal SPI, QSPI, DSPI, and SPI interfaces. Furthermore, it supports the JEDEC SFDP Standard. The IP is designed to allow users to quickly access memory from the xSPI device in SPI mode. Alternatively, users can issue a command to switch to a different mode. Additionally, a DMA command can be used to copy memory from the xSPI device to any other location on the bus.

The DFSPI can automatically drive selected by SSCR (Slave Select Control Register) slave select outputs (SS3O – SS0O), and address SPI slave device to exchange serially shifted data. It supports two DMA modes: single transfer and multi-transfer. These modes allow DFSPI to interface with higher-performance DMA units, which can interleave their transfers between CPU cycles or execute multiple byte transfers. DFSPI is fully customizable, delivering it in the exact configuration that meets users’ requirements.

DCD SPI cores, are part of our growing peripheral family that also includes protocols such as I3C and IR. These cores have been successfully implemented in Embedded Microprocessor Boards, Consumer and Professional Audio/Video, Home and Automotive Radio, Low-power Mobile Applications, Communication Systems, and Digital Multimeters.

More information: https://www.dcd.pl/product/dfspi/

About Digital Core Design

DCD has been founded in 1999 and since the very beginning is focused on IP Core Innovations. During these 25 years company mastered more than 90 different architectures, which have been utilized in more than 750 000 000 electronic devices around the globe. Amin them one can find e.g. World’s Fastest 8051 CPU, World’s Tiniest 8051 IP Core, Royalty-Free and Fully Scalable 32-bit CPU, 100% safe cryptographic system and 32-bit plus 64-bit RISC-V CPUs. More information at dcd.pl

Related Semiconductor IP

- SPI Flash Controller - Ensures reliable validation of SPI Flash memory controllers

- SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption)

- Flash SPI controller master/slave

- Controller IP, SPI Flash controller, Soft IP

- Quad SPI Flash Memory Controller

Related News

- CAST Introduces Microsecond Channel Controller IP Core for Automotive Power and Sensor Interfaces

- DI3CM-HCI, A High-Performance MIPI I3C Host Controller IP Core for Next-Generation Embedded Designs

- Digital Blocks DB9000 Display Controller IP Core Family Extends Leadership in 8K, Automotive, Medical, Aerospace, and Industrial SoC Designs

- TES offers CAN Flexible Data-Rate Controller IP Core for System-on-Chip (SoC) Designs

Latest News

- Menta’s eFPGA Technology Adopted by AIST for Cryptography and Hardware Security Programs

- Silicon Creations Celebrates 20 Years of Global Growth and Leadership in 2nm IP Solutions

- TSMC Debuts A13 Technology at 2026 North America Technology Symposium

- Cadence Collaborates with TSMC to Accelerate Design of Next-Generation AI Silicon

- Synopsys Partners with TSMC to Power Next-Generation AI Systems with Silicon Proven IP and Certified EDA Flows