来自DCD 的 DFSPI IP 核支持市场主流串行存储器

Bytom, Poland -- June 16, 2023 -- Digital Core Design, the leading IP Core provider and System-on-Chip design house, presents its latest DFSPI IP Core for access to NOR and NAND Flash Devices. And if universal NOR & NAND Flash IP is not enough… DCD’s DFSPI IP Core supports also MRAM, pSRAM, DRAM, and EEPROM - combining the ease of use with the reliability, low power, and speed under all conditions, including automotive, industrial, and other applications.

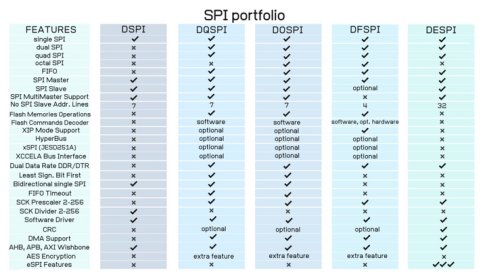

DFSPI IP Core is a real “combo” between all SPI IP Cores available on the market – it’s an SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL, QUAD, OCTAL SPI Bus Controller with DDR / DTR support and optional AES Encryption) + NOR & NAND Flash Memory Support for all serial memories available on the market.

- As an option, the DFSPI controller has a built-in support for HyperBusTM specification and xSPI (Expanded Serial Peripheral Interface – JESD251A) specification – explains Jacek Hanke, DCD CEO The same the SPI Controller allows easy communication with all available SPI FLASH memories.

The DFSP IP Core is compatible with the xSPI JESD251 standard, which can be accessed through a standard AXI4 slave interface. It offers backward compatibility with Octal SPI, QSPI, DSPI, and SPI interfaces. Furthermore, it supports the JEDEC SFDP Standard. The IP is designed to allow users to quickly access memory from the xSPI device in SPI mode. Alternatively, users can issue a command to switch to a different mode. Additionally, a DMA command can be used to copy memory from the xSPI device to any other location on the bus.

The DFSPI can automatically drive selected by SSCR (Slave Select Control Register) slave select outputs (SS3O – SS0O), and address SPI slave device to exchange serially shifted data. It supports two DMA modes: single transfer and multi-transfer. These modes allow DFSPI to interface with higher-performance DMA units, which can interleave their transfers between CPU cycles or execute multiple byte transfers. DFSPI is fully customizable, delivering it in the exact configuration that meets users’ requirements.

DCD SPI cores, are part of our growing peripheral family that also includes protocols such as I3C and IR. These cores have been successfully implemented in Embedded Microprocessor Boards, Consumer and Professional Audio/Video, Home and Automotive Radio, Low-power Mobile Applications, Communication Systems, and Digital Multimeters.

More information: https://www.dcd.pl/product/dfspi/

About Digital Core Design

DCD has been founded in 1999 and since the very beginning is focused on IP Core Innovations. During these 25 years company mastered more than 90 different architectures, which have been utilized in more than 750 000 000 electronic devices around the globe. Amin them one can find e.g. World’s Fastest 8051 CPU, World’s Tiniest 8051 IP Core, Royalty-Free and Fully Scalable 32-bit CPU, 100% safe cryptographic system and 32-bit plus 64-bit RISC-V CPUs. More information at dcd.pl

Related Semiconductor IP

- SPI Flash Controller - Ensures reliable validation of SPI Flash memory controllers

- SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption)

- Flash SPI controller master/slave

- Controller IP, SPI Flash controller, Soft IP

- Quad SPI Flash Memory Controller

Related News

- T2M-IP发布MIPI D-PHY v2.5 Tx和DSI Tx控制器v1.2:针对高级SoC的硅验证、低功耗、经济高效的IP核心解决方案

- CAST 推出 I2C/SPI 控制器 IP 核,实现更加便捷的串行通信方式

- 面向高端汽车电子和消费类应用的CAN XL 控制器 IP 及完整安全套件可立即向客户授权!

- DCD-SEMI 推出用于智能穿戴、音频与移动设备的八进制 SPI IP 核