Alchip Reports ASIC-Leading 2nm Developments

Moving into Rapid Commercial Engagement

Taipei, Taiwan -- Mar 12, 2026 -- Alchip Technologies, Inc., the AI infrastructure and high-performance ASIC leader, today revealed significant development in its commercialization of 2nm customer devices.

The company announced that it’s in design for a full reticle 2nm design and has multiple designs in tape out. It has also refined its groundbreaking 2nm Design Platform. Going further, Alchip acknowledged customer engagements on high performance 2nm full product ASIC development.

In a significant related matter, Alchip has opened its three-dimensional integrated circuit (3DIC) design services and validated its 3DIC ecosystem readiness with results from its 3DIC test chip tape out. The company is also actively fleshing out a proprietary ASIC ecosystem through milestone agreements with a hallmark of technology leaders.

Advanced Designed Platform

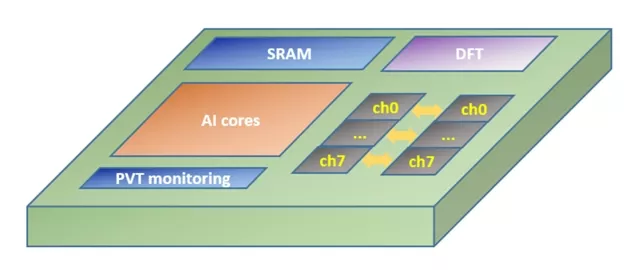

At the heart of the announcement is Alchip 2nm Design Platform that facilitates the physical design of a 2nm chip using multiple types of 2.5D/3D technologies. It supports the development of 5nm or 3nm IO chiplets that work in conjunction with 2nm compute dies. The complete physical design methodology supports technology up to 2nm, and advanced packaging including CoWoS®-S/R/L 2.5D/3D package, System on Integrated Chips (TSMC-SoIC®-X), die-to-die IP, and IO chiplet design. System on Wafer (TSMC-SoW™) 3DIC solutions are on track to be supported as well.

The 2nm process node introduces a complex layout structure, with a significantly greater variety of standard cells that make placement and signal/power routing more challenging. Alchip’s design methodology reduces turnaround time in both design implementation and verification by proactively addressing all side effects before floor planning and clock/power planning stages.

From a packaging standpoint, power density and thermal dissipation per mm2 at the 2nm node are higher because of a larger gate count and faster operating speed. While 2nm IO chiplets are not yet available, Alchip’s 2nm Design Platform provides the more practical approach, enabling 2nm compute dies to work seamlessly with 3nm or 5nm IO chiplets.

Alchip’s 2nm test chips achieved first-pass silicon success, reinforcing the company’s high-performance ASIC leadership. The chip successfully integrated Alchip’s AP-Link-3D I/O IP, demonstrating its readiness for 3D SoIC®-X chiplet applications. The results also lay a foundation for the company’s migration to TSMC’s A14™ process node.

“We’re definitely at the forefront of the AI and high-performance progression to 2nm production. While we’re delighted with this progress, we’re ready to support additional customer 2nm demand. Our 2nm Design Platform clearly showcases our ability to push the boundaries of high-performance computing and artificial intelligence design,” said Johnny Shen, Chairman, CEO, and President of Alchip Technologies.

Alchip’s 2nm test chip targets a gate all-around transistors structure

About Alchip

Alchip Technologies Ltd., founded in 2003 and headquartered in Taipei, Taiwan, is a leading global High-Performance Computing and AI infrastructure ASIC provider of IC and packaging design, and production services for companies developing complex and high-volume ASICs and SoCs. Alchip provides faster time-to-market and cost-effective solutions for SoC design at mainstream and advanced process technology. Alchip has built its reputation as a high-performance ASIC leader through its advanced 2.5D/3D CoWoS packaging, chiplet design, and manufacturing management. Customers include global leaders in artificial intelligence, high-performance computing, supercomputing, mobile communications, entertainment device, networking equipment, and other electronic product categories. Alchip is listed on the Taiwan Stock Exchange (TWSE: 3661).

Related Semiconductor IP

- Band-Gap Voltage Reference with dual 2µA Current Source - X-FAB XT018

- 250nA-88μA Current Reference - X-FAB XT018-0.18μm BCD-on-SOI CMOS

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

Related News

- Alchip Announces Successful 2nm Test Chip Tapeout

- Alchip Introduces 2nm Design Platform

- Open-Silicon Licenses MIPS32(R) 24KEc(TM) Pro Core and Virage Logic Core-Optimized IP Kit for Future ASIC Development

- HiSilicon Expands Cadence Palladium XP Platform Usage For Mobile and Digital Media SoC and ASIC Development

Latest News

- POLYN Technology Announces Tapeout of Automotive Chip

- QuickLogic Establishes New Banking Relationship and Secures $10 Million Revolving Credit Facility

- TES is extending its PMU IP portfolio for X-FAB’s XT018 - 0.18µm BCD-on-SOI technology.

- RF Front-End Modules & Components IP Trends – Q1 2026 Monitoring Release

- IC Manage Advances GDP-AI for Custom IC Design with Virtuoso