Creonic Shows 100 Gbps Polar Decoder in International SENDATE-TANDEM Research Project

Kaiserslautern, Germany, April 10, 2019 – Creonic is pleased to announce its successful participation in the SENDATE-TANDEM (Tailored Network for Data Centers in the Metro) research project, which is a sub-project of the CELTIC SENDATE project. The project ended on March 31, 2019.

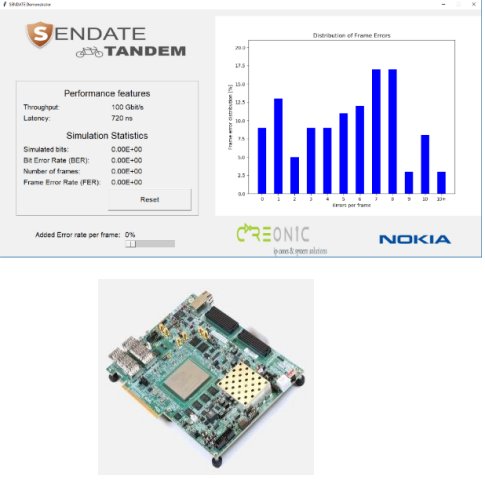

Creonic contributed to the development and demonstration of an advanced forward error correction (FEC) for future ultra high-speed fiber-based transport network architectures. The demonstrator consists of Xilinx Virtex Ultrascale+ FPGA, running a simulation chain with channel emulation and optical loop back for real-time measurements of frame and bit error rate performance of polar codes. It features a list polar decoder with a throughput of 100 Gbps and less than 1 µs of latency.

The project volume of SENDATE is €72.8 millions. The SENDATE-TANDEM consortium consists of 27 partners located in France and Germany. Main industry partners are Nokia Bell Labs France/Germany (former Alcatel-Lucent), Orange, Gemalto, and Thales. The German partners receive funding from the Federal Ministry of Education and Research (BMBF) in Germany.

For more information please visit the SENDATE or SENDATE-TANDEM project pages.

About Creonic

Creonic is an ISO 9001:2015 certified provider of ready-for-use IP cores for several algorithms of communications such as forward error correction (LDPC, Turbo, Polar), modulation, and synchronization. The company offers the richest product portfolio in this field, covering standards like 5G, 4G, DVB-S2X, DVB-RCS2, DOCSIS 3.1, WiFi, WiGig, and UWB. The products are applicable for ASIC and FPGA technology and comply with the highest requirements with respect to quality and performance. For more information please visit our website at www.creonic.com.

Related Semiconductor IP

- 100 Gbit/s Polar Encoder and Decoder with soft-decision LLR input

- 100% Secure Cryptographic System for RSA, Diffie-Hellman and ECC with AMBA AHB, AXI4 and APB

- 12-bit, 100 MSPS Pipeline ADC - X-Fab, 180nm

- Analog Switch, 100 Ohm Typical - HHGrace 110nm

- Analog MUX, Switch Resistance is around 100 Ohm - HHGrace 110nm

Related News

- Creonic Participates in International SENDATE-TANDEM Research Project

- IPrium releases 100 Gbps Polar Encoder and Decoder

- Creonic Participates in National Research Project KI-Radar

- Creonic Participates in H2020 "VERTIGO" Research Project

Latest News

- Analog Bits Demonstrates Real-Time On-Chip Power Sensing and Delivery on TSMC N2P Process at TSMC 2026 Technology Symposiums

- TES offers a High-Frequency Synthesizer and Clock Generator IP for X-FAB XT018 - 0.18µm BCD-on-SOI technology

- Faraday Delivers IP Solutions to Enable Endpoint AI Based on UMC’s 28nm SST eFlash

- AiM Future Partners with Metsakuur Company to Commercialize NPU-Integrated Hardware

- ESD Alliance Reports Electronic System Design Industry Posts $5.5 Billion in Revenue in Q4 2025