Reflex CES' Aurora-Like 64B/66B IP Core Enables Mixed Vendor FPGA Designs

Gives customers the freedom to choose the best FPGA solution

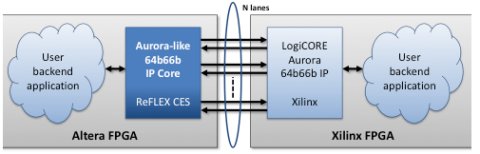

PARIS, France – October 28, 2013 - Reflex CES, a provider of Modified-Off-The-Shelf (MOTS) solutions for embedded and complex systems, today announced the release of its new FPGA Aurora-like 64B/66B IP core, a turnkey solution enabling designers of complex systems to interconnect Xilinx and Altera high speed transceiver FPGAs. Based on Altera FPGAs, the new IP core supports 64B/66B encoding and high-speed interfaces up to 14.4 Gbps, enabling interoperability between Xilinx and Altera FGPAs, with an effective bandwidth of up to 97%.

Targeted specifically at complex, embedded military and telecommunications, networking applications, the 64B/66B FPGA IP core allows designers to choose the most appropriate FPGA solutions to meet their needs, from single or multiple vendors.

“In a complex system with mixed FPGAs, it is always difficult to find a turnkey solution which effectively manages communications using high speed transceiver links,” noted Sylvain Neveu, Reflex CES co-founder and COO.

“With this new IP in our portfolio, engineers are assured interoperability between all leading FPGAs, whatever the performance of their backplanes and systems, from 1 to 14Gbps, and whatever the generic or configurable features incorporated,” he added.

The new IP core offers a fully compliant implementation of the Xilinx Aurora 64B/66bB scalable, link-layer protocol for high-speed serial communication, and allows for communication between FPGAs through a backplane. Based on this open standard protocol used to transport data with higher connectivity performance for chip-to-chip and board-to-board architecture, the Reflex CES Aurora-like 64B/66B IP core allows designers to move data from point-to-point across 1 to 16 serial lanes at up to 14.1 Gbps.

The core features user flow control, native flow control, immediate and completion mode, as well as modules to convert interfaces to and from streaming Advanced eXtensible Interfaces (AXI). This low protocol overhead IP core offers customers minimal data rate transfer latency with minimal logic resources (900 equivalent logic cells for a 4 lane configuration in simplex mode) for cost effective implementation.

Availability

The Reflex CES Aurora-like 8B/10B and Aurora-like 64B/66B IP Cores are available with encrypted or VHDL source code license agreements, encrypted test-benches, reference designs and a user guide.

For pricing information, please contact info_rxc@reflexces.com.

About Reflex CES (Custom Embedded Systems)

Reflex CES is an ISO9001 company designing and manufacturing custom electronic embedded and complex systems. The company specializes in Modified-Off-The-Shelf (MOTS) solutions for high-speed boards and rugged systems solutions based on high density FPGAs. Solutions delivered include: CPU, processing or acquisition boards or complete chassis, high speed data recorders, FPGA SoC, ASIC prototyping platforms. Reflex CES is member of the Altera Design Services Network and Freescale Alliance. For more information about Reflex CES, please visit http://www.reflexces.com/en/

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- MIPI CSI-2 CSE2 Security Module

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

Related News

- CAST Expands Security IP Portfolio with High Performance SM4 Cipher Core

- Creonic Updates Doppler Channel IP Core with Extended Frequency Band and Sampling Range

- DCD-SEMI Brings Full ASIL-D Functional Safety to Entire Automotive IP Cores Portfolio

- Kerala Positions Design and IP at Core of Chip Strategy

Latest News

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3

- Xylon Presents New 12-Channel GMSL3/GMSL2 FMC+ ExpansionBoard