SR-IOV IP

Filter

Compare

99

IP

from

14

vendors

(1

-

10)

-

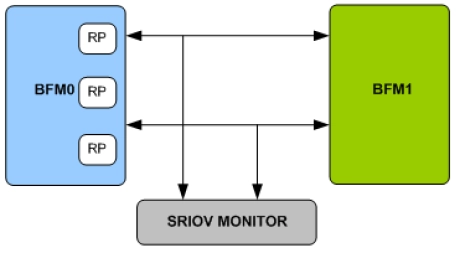

SRIOV Verification IP

- Supports SRIOV specs 1.0/1.1.

- Supports PCIE Express specs 1.0/2.0/3.0/4.0/5.0.

- Supports PIPE, Serial, PCS/PMA, Low pin count and SerDes interface.

- Supports UVM and Verilog APIs supplied , as well as C DPI exports

-

CXL Controller

- Compliant with CXL Specification version 2.0/1.1 and PCIe Base Specification 5.0 (32 Gbps per lane)

- Complaint with PIPE 5.x interface

- Supports X16, X8, X4, X2 and X1 lane widths

- Supports 512, 256 and 128 Data path widths

- Supports PCI Express Alternate Protocol

-

PCIe Controller

- Compliant to PCI Express base specification 5.0 (32 Gbps per lane) and backward compatible with PCI Express versions 4.0, 3.1, 2.0 and 1.1

- Supports configurable number of PFs and VFs for SR-IOV

- Architected for high link utilization and low latency

- Efficient receive and transmit-retry buffering scheme

-

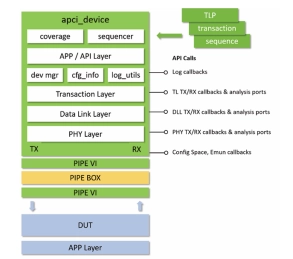

Verification IP for PCIe

- Accelerated confidence in simulation-based verification of RTL designs with PCI Express (PCIe) interfaces: PCIe Gen2/3/4/5/6/7

-

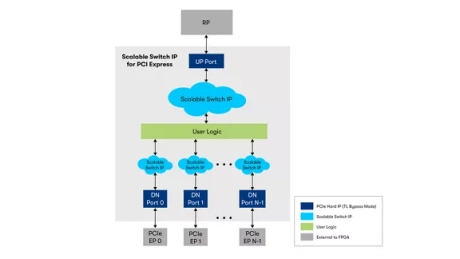

Scalable Switch Intel® FPGA IP for PCI Express

- The Scalable Switch Intel® FPGA IP for PCI Express is a fully configurable switch that implements one fully configurable upstream port and connectivity for up to 64 downstream ports.

-

R-Tile PCIe Hard IP

- R-Tile is a FPGA companion tile that supports configurations up to PCIe 5.0 x16 in Endpoint (EP), Root Port (RP), and Transaction Layer (TL) Bypass modes

- PCIe 3.0, 4.0, and 5.0 configurations are natively supported

- R-Tile also supports up to 16 SerDes channels through a PHY Interface for PCIe (PIPE) 5.1.1 in SerDes Architecture mode.

-

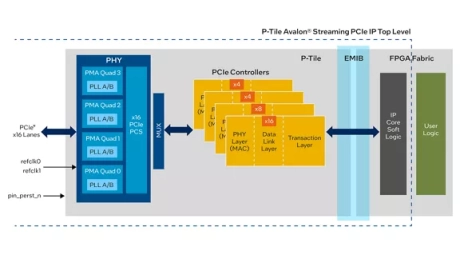

P-Tile PCIe* Hard IP

- P-Tile is an FPGA companion tile available on Stratix® 10 DX and Agilex™ 7 FPGA F-Series device that natively supports PCIe* configurations up to 4.0 x16 in Endpoint (EP), Root Port (RP), and Transaction Layer (TL) Bypass Modes.

-

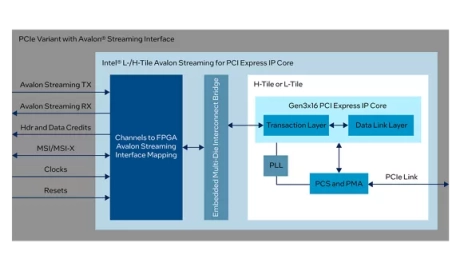

L/H-Tile PCIe Hard IP

- Stratix® 10 FPGAs incorporate the L/H-Tile chiplets which include a configurable, hardened protocol stack for PCIe that is compliant with PCIe Base Specification 3.0

- This Avalon® Streaming Interface Hard IP supports PCIe 1.0, 2.0, and 3.0 data rates and x1, x2, x4, x8, or x16 configurations, including support for SR-IOV functionality.

-

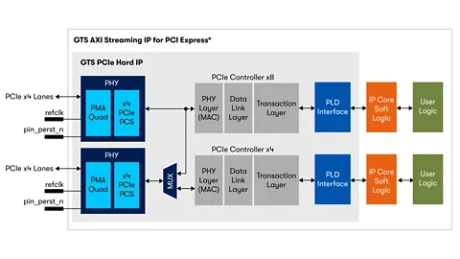

GTS PCIe Hard IP

- Agilex™ 5 FPGAs and SoC FPGAs are monolithic designs with integrated high-speed transceivers (GTS) and hardened PCIe controller IP supporting up to PCIe 4.0 x8 configurations for Root Port (RP), Endpoint (EP), and Transaction Layer (TL) bypass modes.

- GTS PCIe Hard IP for PCI Express Greatly Simplifies Design Integration for a Broad Range of Applications

-

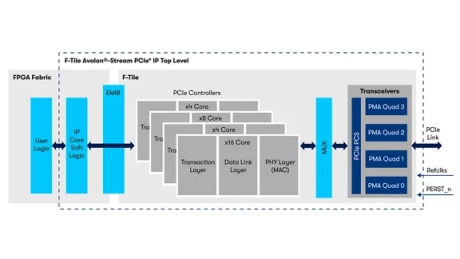

F-Tile PCIe Hard IP

- The F-Tile Intel® Hard IP supports PCIe* configurations up to 4.0 x16 in Endpoint (EP), Root Port (RP), and Transaction Layer (TL) Bypass Modes

- F-Tile serves as a companion tile for Agilex™ 7 devices.