MIPI M-PHY 4.1 IP

Filter

Compare

13

IP

from

5

vendors

(1

-

10)

-

Simulation VIP for MIPI M-PHY

- Specification Compliance

- Complies with MIPI M-PHY 4.0, 4.1 and 5.0 specification

- M-PHY Type 1 and Type 2

- Supports Type 1 and Type 2

-

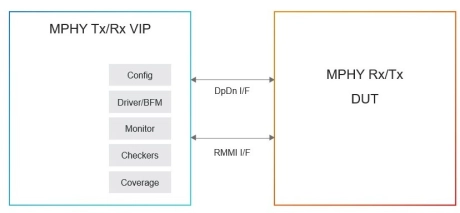

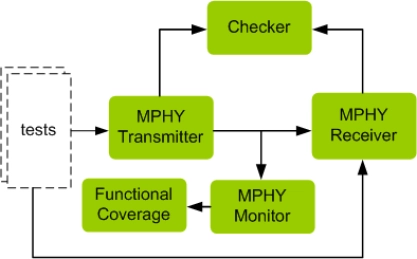

MIPI MPHY Verification IP

- Supports 3.0,4.1 and 5.0 MIPI MPHY Specification.

- Support Type-1 and Type-II operations.

- Supports both serial and protocol layer interface.

- Supports all PWM 0-7 gear of operation.

-

MIPI M-PHY v4.1 IP, Silicon Proven in UMC 28 HPC

- Compliant with M-PHY Spec 4.1, UniPro Spec 1.8, UFS Spec 3.0

- Support HS-MODE Gear4(A/B) with data rate up to 11.6Gb/s, and backward compatible

-

MIPI M-PHY v3.1 IP, Silicon Proven in UMC 40LP

- Compliant with M-PHY Spec 4.1, UniPro Spec 1.8, UFS Spec 3.0

- Support HS-MODE Gear4(A/B) with data rate up to 11.6Gb/s, and backward compatible

- Support LS-MODE PWM-G1 to PWM-G5 with data rate up to 144Mb/s

- Support reference clock frequency with 19.2/26/38.4/52MHz defined in UFS spec.

-

MIPI M-PHY v4.1 IP, Silicon Proven in TSMC 12FFC

- Compliant with M-PHY Spec 4.1, UniPro Spec 1.8, UFS Spec 3.0

- Support HS-MODE Gear4(A/B) with data rate up to 11.6Gb/s, and backward compatible

- Support LS-MODE PWM-G1 to PWM-G5 with data rate up to 144Mb/s

- Support reference clock frequency with 19.2/26/38.4/52MHz defined in UFS spec.

-

MIPI M-PHY HS Gear 4 IP

- Supports high speed data transfer G4A/B and backward compatible

- Multi-lane compatible

- Supports 4 reference clocks as per MIPI 4.1 specification

- PWM G1-G7 Signalling for Low Speed [LS] data

- Supports LS burst, HS burst, STALL, SLEEP, HIBERN8 states

- Supports squelch detection

-

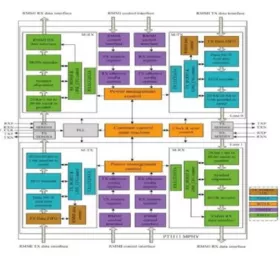

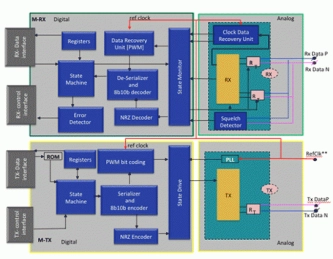

MIPI M-PHY® 4.1 Analog Transceiver

- The M-PHY is of Type 1, which apply to UFS, LLI, and CSI-3 protocols. The Multi-gear M-PHY 4.1 consists of analog transceivers, high-speed PLL, data recovery units as well as state-machine control — all in a single GDSII.

- The interface to the link protocol-specific controller (host or device) is compliant with the M-PHY RMMI specification, which allows seamless integration of the two IPs, namely the controller and the PHY, into the chip design.

-

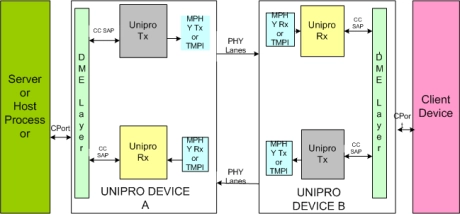

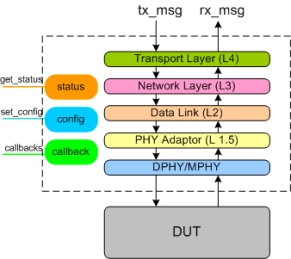

MIPI UniPro Verification IP

- Supports MIPI UniPro specification 1.41,1.6,1.8 and 2.0.

- Support MIPI MPHY specification 3.0,4.1 and 5.0.

- Supports data control at each layer of UniPro Specification for easy debug.

- Supports multiple connections in L4 Layer and L4 segments.

-

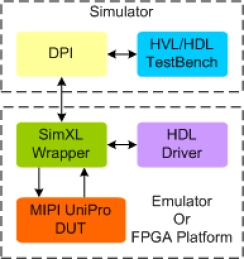

MIPI Unipro Synthesizable Transactor

- Supports MIPI UniPro specification 1.41, 1.6 and 1.8

- Supports MIPI MPHY specification 3.0 and 4.1

- Supports data control at each layer of UniPro Specification for easy debug

- Supports multiple connections in L4 Layer and L4 segments

-

MIPI UniPro IIP

- Compliant with MIPI UNIPRO specification version 1.6,1.8 and 2.0

- Supports MIPI M-PHY specification 3.0 ,4.1 and 5.0

- Supports multiple connections in L4 Layer and L4 segments

- Supports M-PHY HS data rates HS-Gear1 – Gear5, both A/B modes and PWM