Codasip IP

Filter

Compare

11

IP

from

1

vendors

(1

-

10)

-

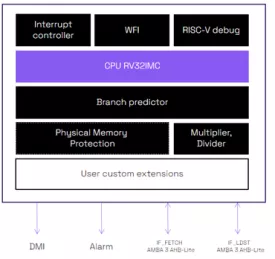

32 Bit - Embedded RISC-V Processor Core

- Best-in-class performance for small-area and low-power applications

- Highly configurable and easy and quick to customize and verify

- Process compliant with ISO 26262 and ISO 21434

-

-

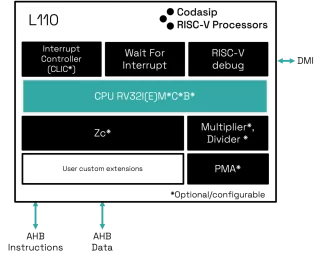

32 bit - Compact RISC-V Processor Core

- 32-bit RISC-V core

- RV32EMC instruction set

- 16 general purpose registers

-

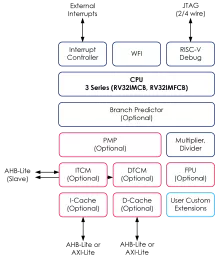

Compact RISC-V Processor - 32 bit, 3-stage pipeline, 32 registers

- 32-bit RISC-V core

- Available in two versions:

- 32 general purpose registers

- Either parallel multiplier

-

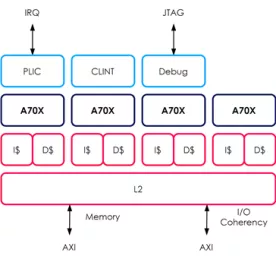

64-bit RISC-V Application Processor Core

- High computational throughput with 7-stage pipeline and branch predictor

- Support for RISC-V single and double precision FPU

-

-

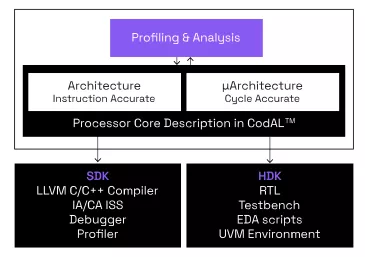

Processor Development Toolset

- A unified development model describing the processor in a single CodAL description

- High performance processor synthesis

- Complete UVM verification environment

- Advanced profiling and analysis

-

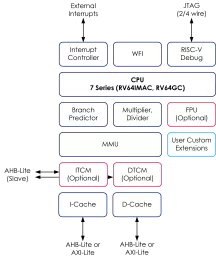

Compact, efficient 64-bit RISC-V processor with 5-stage pipeline

- Support for RV32IM

- 5-stage pipeline

- Thirty-two 64-bit general purpose registers

-

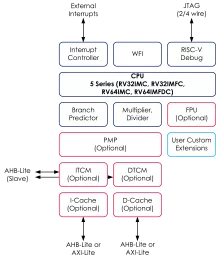

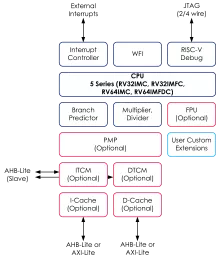

RISC-V processor - 32 bit, 5-stage pipeline

- Support for RV32IM/RV64IM

- 5-stage pipeline

- 32 or 64bit general purpose registers

-

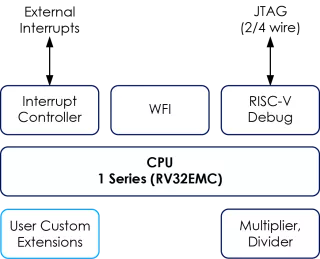

32-bit RISC-V embedded processor with TÜV SÜD ISO 26262 ASIL B certification

- Flexible use cases

- roven technology

- State-of-the-art safety and security