Peripheral IP for TSMC

Welcome to the ultimate

Peripheral IP

for

TSMC

hub! Explore our vast directory of

Peripheral IP

for

TSMC

All offers in

Peripheral IP

for

TSMC

Filter

Compare

7

Peripheral IP

for

TSMC

from

3

vendors

(1

-

7)

Filter:

- 28nm

-

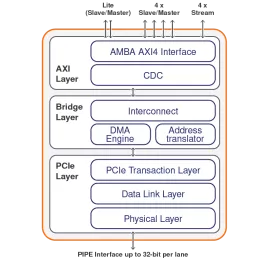

PCIe 3.1 Controller with AXI

- Compliant with the PCI Express 3.1/3.0, and PIPE (16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode configurations

- Supports x16, x8, x4, x2, x1 at 8 GT/s, 5 GT/s, 2.5 GT/s speeds

- Supports AER, ECRC, ECC, MSI, MSI-X, Multi-function, P2P, crosslink, and other optional features

- Supports many ECNs including LTR, L1 PM substates, etc.

-

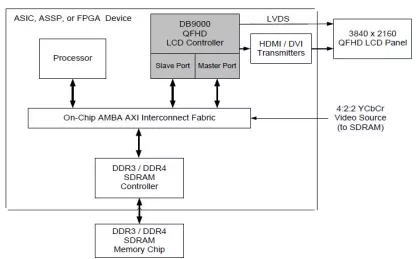

Display Controller – 4K Digital Cinema LCD Panels (AXI4/AXI Bus)

- The DB9000AXI-DCI LCD Controller IP Core interfaces a video image in frame buffer memory via the AMBA 3.0 / 4.0 AXI Protocol Interconnect to a 4K and 2K Digital Cinema Initiative (DCI) High Definition TFT LCD panel

- The video image in frame buffer memory can be 8/10/12-bit YCrCb or RGB, with a Color Space Convert to match the source video to the TFT LCD panel requirements

-

Camera Combo Receiver - 2.4Gbps 8-Lane - TSMC 28nm HPC

- The CL12832M8R2JM3KIP2400 is designed to support data rate in excess of maximum 2.4Gbps utilizing SLVS-EC / sub-LVDS / CMOS 1.8V interface specification.

- The CL12832M8R2JM3KIP2400 can change Interface type to same PAD for changing mode.

-

MIPI D-PHY Transmitter 4-Lane (4-Data/1-Clock) 250Mbps

- The CL12631I4T1AS1BIP2500 is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to Host System.

- The CL12631I4T1AS1BIP2500 converts the input parallel data to the serial data and output it.

- The CL12631I4T1AS1BIP2500 is designed to support maximum 2.5Gbps data rate utilizing mipi-DPHY_specification_v1-2.

-

MIPI D-PHY/sub-LVDS Transmitter - 8-Lane 2.5Gbps - TSMC 28nm HPC+

- The CL12661M8T1KM2JIP is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to Host System.

- The CL12661M8T1KM2JIP is designed to support data rate in excess of maximum 2.5Gbps utilizing sub-LVDS / MIPI-DPHY interface specification.

-

Camera Combo Receiver - 2.4Gbps 8-Lane - TSMC 28nm HPC

- The CL12842M8R2JM4TIP2500 is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to ISP (Imaging Signal Processer) and DSP.

- The CL12842M8R2JM4TIP2500 is designed to support data rate in excess of maximum 2.5Gbps utilizing SLVS-EC / sub-LVDS / MIPI D-PHY v-1.2/ CMOS 1.8V interface specification.

-

Camera 6/7-mode Combo Receiver - 1G/1.5Gbps

- The CL12684KM4-8-12-16R3AM6-7ZIP is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to Host System.

- The CL12684KM4-8-12-16R3AM6-7ZIP is designed to support data rate in excess of maximum 1Gbps utilizing sub-LVDS / mini-LVDS / LVDS / HiSPi(SLVS-400, HiVCM) / MIPI-DPHY / CMOS-1.8V / CMOS-3.3V interface specification.