MIPI M-PHY IP for TSMC

Welcome to the ultimate

MIPI M-PHY IP

for

TSMC

hub! Explore our vast directory of

MIPI M-PHY IP

for

TSMC

All offers in

MIPI M-PHY IP

for

TSMC

Filter

Compare

6

MIPI M-PHY IP

for

TSMC

from

4

vendors

(1

-

6)

Filter:

- 28nm

-

MIPI M-PHY IP

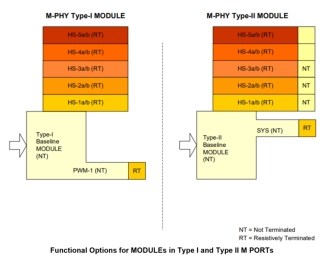

- The MIPI M-PHY is a high-frequency low-power, Physical Layer IP that supports the MIPI® Alliance Standard for M-PHY.

- The IP can be used as a physical layer for many applications, connecting flash memory-based storage, cameras and RF subsystems, and for providing chip-to-chip inter-processor communications (IPC).

-

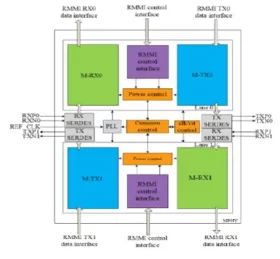

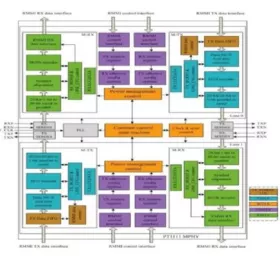

MIPI MPHY v3.1, 2Tx-2Rx Type-1, TSMC 28HPC+, N/S orientation

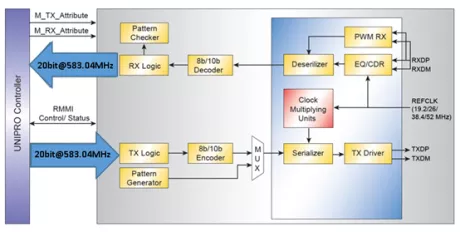

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions

-

MIPI M-PHY v4.1 IP, Silicon Proven in TSMC 28 HPC+

- RX:DFE+CTLE, TX:2-tap FFE

- Max. Channel Loss:~14dB @6GHz Nyquist

- Low operation current and low standby current

-

MIPI M-PHY v3.1 IP, Silicon Proven in TSMC 28HPC+

- Compliant with M-PHY Spec 3.0

- Support HS-MODE Gear3(A/B) with data rate up to 5.8Gb/s, and backward compatible

- Support LS-MODE PWM-G1 to PWM-G4 with data rate up to 72Mb/s

- Support reference clock frequency with 19.2/26/38.4/52MHz defined in UFS spec

-

MIPI M-PHY HS Gear 4 IP

- Supports high speed data transfer G4A/B and backward compatible

- Multi-lane compatible

- Supports 4 reference clocks as per MIPI 4.1 specification

- PWM G1-G7 Signalling for Low Speed [LS] data

- Supports LS burst, HS burst, STALL, SLEEP, HIBERN8 states

- Supports squelch detection

-

MIPI M-PHY v3.1 IP in TSMC(12/16nm, 28nm, 40nm, and 55nm)

- Supports RMMI interface for applications such as UNIPRO protocol (UFS, CSI-3, DSI-2) and DigRF

- High speed gears, HS-G1A/B, HS-G2A/B and HS-G3A/B with scalable power consumptions

- Burst mode CDR with short sync length (< 16SI)

- Low speed PWM Gears from G1 to G4 with ultra-low power consumptions