MIPI IP for TSMC

Welcome to the ultimate

MIPI IP

for

TSMC

hub! Explore our vast directory of

MIPI IP

for

TSMC

All offers in

MIPI IP

for

TSMC

Filter

Compare

222

MIPI IP

for

TSMC

from

12

vendors

(1

-

10)

-

MIPI D-PHY and FPD-Link (LVDS) Combinational Transmitter for TSMC 22nm ULP

- Technology is TSMC 22nm ULP 1p10M.

- Supply voltage can be applied 1.0V for core voltage, 1.8V for IO voltage.

- Maximum data rate of each channel is 1.5Gbps at High-speed mode for MIPI D-PHY Transmitter.

- Data rate of each channel is 609Mbps for FPD-Link(LVDS).

-

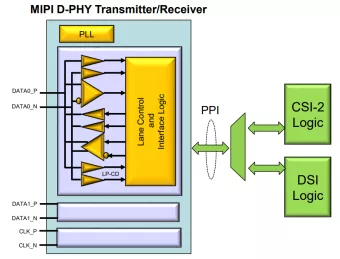

MIPI D-PHY Transmitter/Receiver for TSMC 40nm LP

- Renesas MIPI D-PHY Transmitter/Receiver can be used for analog Transmitter/Receiver of following interface.

- Technology is TSMC 40nm LP 1p6M (4x1z) .

- Supply voltage can be applied 1.1V for core voltage, 1.8V for IO voltage.

-

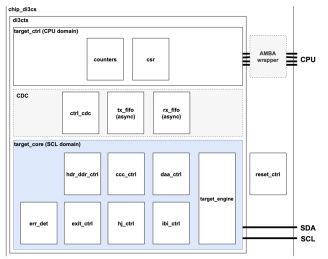

MIPI I3C Target Device

- MIPI I3C Basic Specification v1.2 compiliance

- Native 32-bit CPU Interface

- Optional CPU interface wrappers (APB, AHB, AXI)

- Legacy I2C communication with 7-bit Static Address

- I3C Single Data Rate (SDR) mode

-

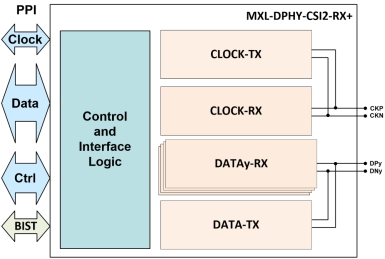

MIPI D-PHY RX+ (Receiver) IP

- The MIPI® D-PHY RX+ is a proprietary implementation of the MIPI Camera Serial Interface 2 (CSI-2) and Display Serial Interface (DSI) D-PHY Receiver.

- It is optimized to achieve full-speed production testing, in-system testing, and higher performance compared to traditional configurations, while reducing area and standby power.

-

MIPI D-PHY/LVDS Combo Receiver IP

- The MXL-LVDS-MIPI-RX is a high-frequency, low-power, low-cost, source-synchronous, Physical Layer that supports the MIPI® Alliance Standard for D-PHY and compatible with the TIA/EIA-644 LVDS standard.

- The IP is configured as a MIPI slave and consists of 5 lanes: 1 Clock lane and 4 data lanes, which make it suitable for display serial interface applications (DSI).

-

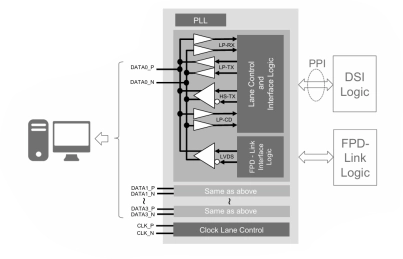

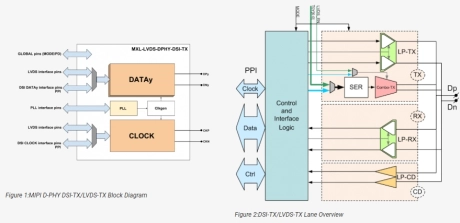

MIPI D-PHY/LVDS Combo Transmitter IP

- The MXL-LVDS-DPHY-DSI-TX is a combo PHY that consists of a high-frequency low-power, low-cost, source-synchronous, Physical Layer supporting the MIPI® Alliance Standard for D-PHY and a high performance 4-channel LVDS Serializer implemented using digital CMOS technology.

- In LVDS mode, both the serial and parallel data are organized into 4 channels. The parallel data is 7 bits wide per channel. The input clock is 25MHz to 150MHz. The serializer is highly integrated and requires no external components. The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

-

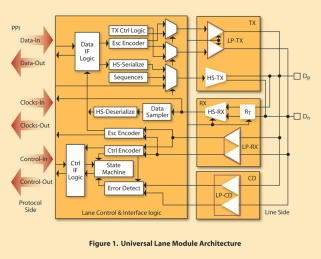

MIPI D-PHY IP

- The D-PHY is partitioned into a Digital Module – CIL (Control and Interface Logic) and a Mixed Signal Module. It is provided as a combination of Soft IP views (RTL, and STA Constraints) for Digital Module, and Hard IP views (GDSII/CDL/LEF/LIB) for the Mixed Signal Module.

- This unique offering of Soft and Hard IP permits architectural design flexibility and seamless implementation in customer-specific design flow.

-

MIPI M-PHY IP

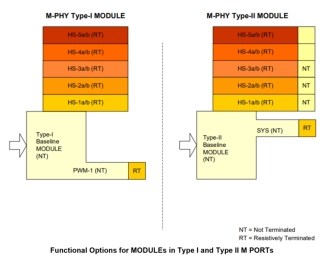

- The MIPI M-PHY is a high-frequency low-power, Physical Layer IP that supports the MIPI® Alliance Standard for M-PHY.

- The IP can be used as a physical layer for many applications, connecting flash memory-based storage, cameras and RF subsystems, and for providing chip-to-chip inter-processor communications (IPC).

-

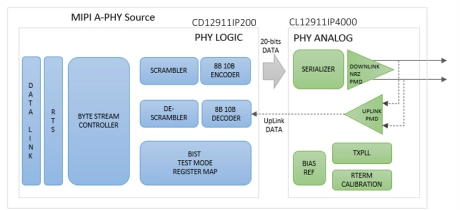

Sensor / Display MIPI A-PHY Source IP

- The CL12911IP4000 is based on MIPI A-PHY interface specification announced in year 2020, targeting ultra-high-speed networking applications in ADAS and autonomous drive subsystems.

- It supports applications that require long reach (up to 15 meters), error-free links, and high EMI immunity requirement.

-

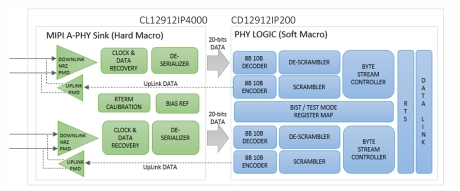

Sensor/Display MIPI A-PHY Sink IP

- The CL12912IP4000 is based on MIPI A-PHY interface specification announced in year 2020, targeting ultra-high-speed networking applications in ADAS and autonomous drive subsystems.

- It supports applications that require long reach (up to 15 meters), error-free links, and high EMI immunity requirement.