Analog IP for SMIC

Welcome to the ultimate

Analog IP

for

SMIC

hub! Explore our vast directory of

Analog IP

for

SMIC

All offers in

Analog IP

for

SMIC

Filter

Compare

437

Analog IP

for

SMIC

from

19

vendors

(1

-

10)

-

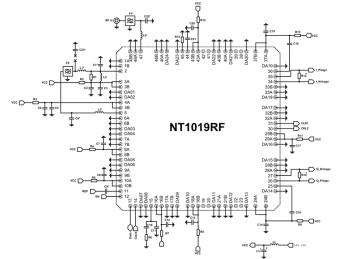

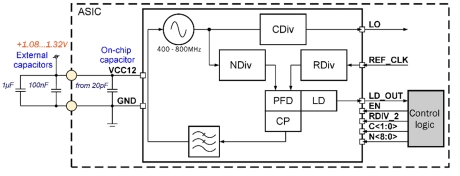

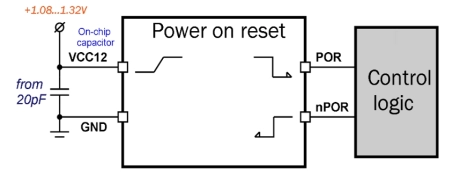

50MHz to 800MHz Integer-N RC Phase-Locked Loop on SMIC 55nm LL

- 055SMIC_PLL_01 forms clock output signal with frequency from 50 to 800MHz.

- It consists of the ring VCO with frequency from 400 to 800MHz, a programmable feedback divider, a low noise digital phase noise detector (PFD), a precision charge pump (CP) with internal loop filter, lock detector (LD) and programmable clock divider to obtain a required output frequency.

- LO output signal is CMOS compatible.

-

-

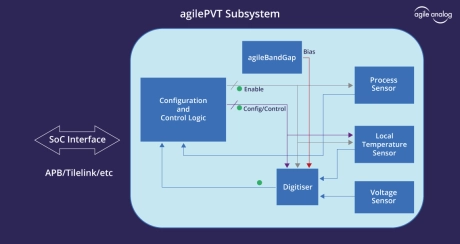

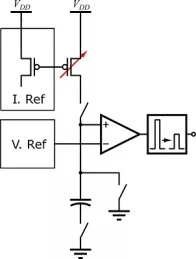

PVT Sensor Subsystem

- Start-up time: Typ 20us

- Current consumption: Max 25uA

- Industry standard digital interface

- Fully integrated macro

- Standard AMBA APB interface

-

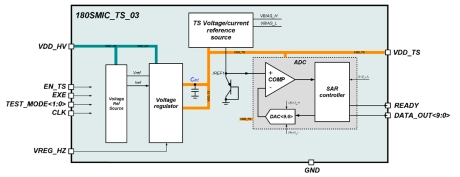

-40°C to +85°C Low power temperature sensor

- The 180SMIC_TS_03 is a unique stand-alone solution intended to continuously monitor IC status.

- Temperature detector consists of temperature sensor unit (the voltage at which is directly proportional to the temperature), analog core, SAR controller as calculation center for temperature measurements, as well as an internal voltage regulator, with an output level of 1.25V.

-

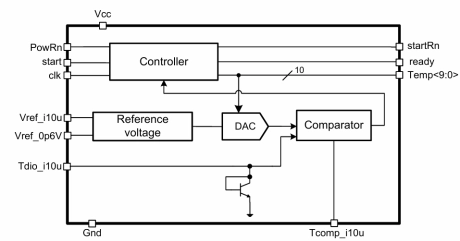

Temperature sensor

- SMIC CMOS 0.18 um

- Output voltage 1.2 V

- Temperature-compensated voltage in a wide temperature range

- Low current consumption

-

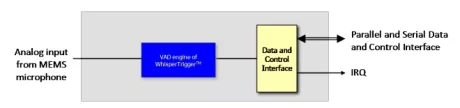

Always-on Voice Activity Detection interfacing with analog microphones

- Voice activity detector enables drastic reduction in power consumption

- Self-adjustment to background noise

- Ambient Noise sensing

-

Always-on Voice Activity Detection interfacing with analog microphones

- Voice activity detector enables drastic reduction in power consumption

- Self-adjustment to background noise

- Ambient Noise sensing

-

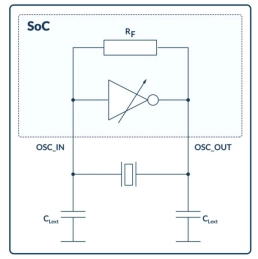

Crystal Oscillators

- The crystal oscillator macros are available in a wide range of industry-standard quartz crystals and MEMS resonators operating in the fundamental mode in the 32 kHz to 80 MHz range.

- These oscillators, which are both power and area efficient, have a programmable transconductance to allow users to find the optimal balance between jitter and power consumption.

-

Free running oscillators

- Compact and low power

- No external components

- Baseline CMOS logic process masks only

- Excellent frequency precision over PVT after trimming

-

GPS/Galileo/GLONASS multisystem single-band receiver

- SMIC RF CMOS 180 nm technology

- Single conversion superheterodyne receiver