I/O Library IP for Silterra

Welcome to the ultimate

I/O Library IP

for

Silterra

hub! Explore our vast directory of

I/O Library IP

for

Silterra

All offers in

I/O Library IP

for

Silterra

Filter

Compare

10

I/O Library IP

for

Silterra

from

2

vendors

(1

-

10)

-

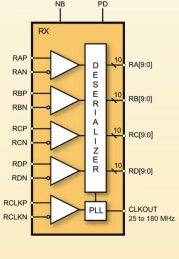

LVDS Deserializer IP

- The MXL-DS-LVDS is a high performance 4-channel LVDS Deserializer implemented using digital CMOS technology.

- Both the serial and parallel data are organized into four channels. The parallel data can be 7 or 10 bits wide per channel. The input clock is 25MHz to 165MHz. The De-serializer is highly integrated and requires no external components.

-

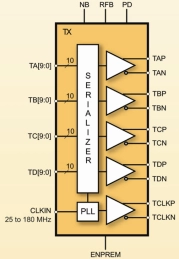

LVDS Serializer IP

- The MXL-SR-LVDS is a high performance 4-channel LVDS Serializer implemented using digital CMOS technology. Both the serial and parallel data are organized into four channels.

- The parallel data width is programmable, and the input clock is 25MHz to 165MHz. The Serializer is highly integrated and requires no external components.

-

LCD Host LVDS Interface, Dual Pixel 20-112Mhz (SVGA/QXGA)

- 1P6M layout structure based on 0.18um 1P6M 1.8V generic logic process.

- 3.3V/1.8V ±10% supply voltage, -40/+125°C

- Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard 1596.3-1996+ ANSI/TIA/EIA-644-A Specifications.

- Up to 5.38Gbps bandwidth

-

Dual FPD-link, 30-Bits Color LVDS Receiver, 170Mhz (SVGA/FHD@120Hz) LVDS de-serializer 10:70 channel decompression with automatic de-skew

- Layout structure based on 0.13um Logic 1P6M, 1P7M, or 1P8M Salicide 1.2V/3.3V process.

- 1.2V/3.3V ±10% supply voltage, -40/+125°C

- Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard 1596.3- 1996+ ANSI/TIA/EIA-644-A Specifications.

- Up to 11.9Gbps bandwidth (40 to 170Mhz pixel clock) per pixel channel (Full HD @ 120Hz)

-

Dual RSDS Transmitter, 30-bit color, 40-300Mb/s (SVGA/UXGA/full HDTV) LCD & Plasma display

- • 20 to 150 Mhz Pixel rate per channel ( 40 to 300 Mb/s SDR input, 40 to 300 Mb/s DDR output )

- • 30 DATA + 9 RSDS CLK channels

- • Complies with RSDS “Intra-Panel” Interface Specification rev1.0, May 2003.

- • 1P6M layout structure based on 0.18um 1P6M generic logic process.

-

Dual RSDS Transmitter, 24/18-bit color, 40-300Mb/s (SVGA/UXGA/full HDTV) LCD & Plasma display

- • 20 to 150Mhz Pixel rate ( 40 to 300 Mb/s SDR input, 40 to 300 Mb/s DDR output)

- • Complies with RSDS “Intra-Panel” Interface Specification rev1.0, May 2003.

- • 1P6M layout structure based on 0.18um 1P6M generic logic process.

- • 3.3V/1.8V 10% supply voltage, -40/+125C

-

LVDS Transmitter 1250Mb/s, 800Mhz clock with RSDS support

- • 1P6M layout structure based on 0.18um 1P6M 1.8V

- generic logic process.

- • 3.3V/1.8V ±10% supply voltage, -40/+125°C temperature.

- • IEEE Standard 1596.3-1996 and ANSI/TIA/EIA- 644-A Specifications.

-

LVDS Receiver 1250Mb/s, 800Mhz clock

- • 1P6M layout structure based on 0.18um 1P6M 1.8V generic logic process.

- • 3.3V/1.8V ±10% supply voltage, -40/+125°C temperature.

- • IEEE Standard 1596.3-1996 and ANSI/TIA/EIA-644-A Specifications.

- • Up to 1250Mb/s DDR, or 800Mhz clock.

-

Dual FPD-link Transmitter, 24 Bits Color, 20-170 Mhz (SVGA/UXGAW/Full HDTV)

- • 1P6M layout structure based on 0.13um 1P6M 1.8V/3.3V generic logic process.

- • 3.3V/1.8V ±10% supply voltage, 0/+125°C

- • Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard

- 1596.3-1996+ ANSI/TIA/EIA-644-A Specifications.

-

FPD-link, 30Bits Color LVDS Receiver, 150Mhz (SVGA/WXGA)

- 1P6M layout structure based on 0.18um 1P6M 1.8V generic logic process.

- 3.3V/1.8V 10% supply voltage, 0/+125C

- Complies with OpenLDI specification for digital display interfaces and LVDS IEEE Standard 1596.3-1996+ ANSI/TIA/EIA-644-A Specifications.

- Up to 3.15Gbps bandwidth (8 to 90Mhz pixel clock for 1 channel)