Why Standard-Cell Architecture Matters for Adaptable ASIC Designs

The Only eFPGA That Is 100% Standard-Cell — No Proprietary Macros with Hidden Risk

By Menta

Why the World’s Most Demanding ASICs and SoCs Choose Menta eFPGA

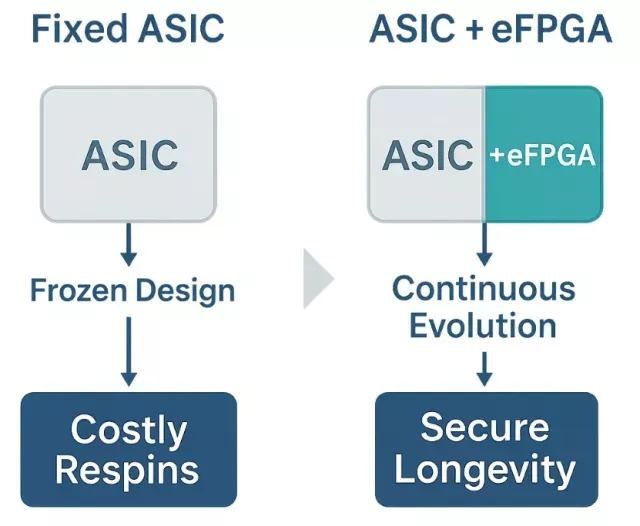

The semiconductor industry has long accepted a painful tradeoff — ASICs for efficiency and cost, or discrete FPGAs for flexibility. But that tradeoff is over. Menta’s embedded FPGA (eFPGA) delivers reconfigurable intelligence inside your ASIC — with zero compromise on foundry portability, standard-cell safety, PPA optimization, yield or testability.

There is only one eFPGA architecture that fully behaves like ASIC logic — and that’s a 100% standard-cell implementation. No proprietary macros, no SRAM bitcells, no external configuration infrastructure. Menta’s approach maps directly into any foundry, any process, and any cell library — including rad-hard, automotive safety, low-leakage industrial, and beyond. Standard-cell is the only path that guarantees verifiable full test coverage, long-term reliability, and zero vendor macro dependency. And a standard-cell implementation accelerates time-to-market by enabling solutions to be created immediately — without the delay or risk of developing custom hard macros.

What true portability and true autonomy means:

- Foundry and Node Agnostic — Menta integrates at TSMC, Global Foundry, Samsung, Intel, IDMs and any other CMOS fabs, including specialty aerospace/automotive fabs with no requalification process.

- No custom IP dependencies — nothing black-box, nothing proprietary — it’s all built from the same library cells you already trust.

- Compatible with rad-hard, automotive, industrial, or low-power libraries — select the library you need, and Menta maps natively into it.

You own the silicon. You control the IP. You never depend on a vendor’s “secret sauce.”

Menta behaves exactly like your ASIC logic. Because it is ASIC logic.

- Predictable timing — no fabric clocking unpredictability

- Standard ASIC Test Flow — 99.7%+ coverage with your ATPG tools

- Yield, burn-in, electromigration — all covered using your sign-off tools

- Rapid design agility — no reliance on custom hard macros

Every Customer Gets Their Own PPA-Optimized eFPGA

If your eFPGA cannot be verified, signed off, and qualified like any other standard digital block — it doesn’t belong in your ASIC. That’s why Menta’s architecture is built entirely from native standard-cells, ensuring 99.7%+ test coverage, full access to foundry-certified reliability models, and seamless integration into automotive, industrial, medical or space-grade flows. Reconfigurable logic without compromising ASIC integrity is not a dream — it’s the only architecture we ship.

Unlike fixed-architecture eFPGA products, Menta allows per-customer tuning at the silicon level before tapeout:

- Choose high-speed cells for GHz-class operation or low-leakage cells for always-on sensor hubs

- Mix voltage thresholds freely (Multi-Vt) — no architectural limitation

- Use your own power grid strategy, your own voltage islands, your own thermal & aging models

- Sign off using your own PPA/adaptation tools — not someone else’s backend flow

- Everything can be simulated, down to gate level, using the models you already trust – not the eFPGA IP provider own models

This is not “one size fits all.” This is your silicon, optimized for your application, with future optionality built in. And after all, PPA control is strategic control!

And the Competition?

Some eFPGA vendors promote area savings using full custom designs or semi-custom designs with various mixes of proprietary bitcells, custom muxes and proprietary SRAM blocks. First, let’s be clear, there is little to no area saving with this approach, mainly because these custom cells require compromises to avoid for yield losses.

Second, they introduce massive, hidden risks. Persistent configuration memory, qualification complexity, black-box macros, and limited testability are fundamentally incompatible with long-life, safety-critical, and sovereign silicon. Menta’s standard-cell architecture avoids every one of those pitfalls — while still enabling reconfigurability, performance tuning, and voltage domain flexibility with zero compromise to safety or trust. Any custom design is by essence an analog design – which requires careful Monte Carlo simulations and, as they are not natively supported by the Foundry, are prone to failure with any process recipe evolution or process deviations. Don’t be stuck with vendors with IP that includes:

- Black-box macros with limited test coverage

- No access to specialty cell libraries (rad-hard, low-leakage, automotive-grade and MIL-grade, etc.)

- Non-standard signoff flows and aging models

And while some of these vendors claim minor area savings — typically just a few single-digit percentage points — those gains, if real at all, are not worth sacrificing silicon sovereignty, certification simplicity, or long-term trust. Menta eliminates this tradeoff entirely with a highly optimized configuration memory architecture that reduces configuration density by up to 75%, easily outperforming any theoretical hard-macro “area advantage” claimed by custom or SRAM-based eFPGA vendors. Menta third party standard cells based eFPGA are in essence guaranteed by the sign-off flows and elements from foundries and specialty providers.

The Bottom Line

Menta eFPGA delivers the only reconfigurable fabric that behaves like standard ASIC logic — but evolves like software. In markets where security and long-term reliability matter — the future belongs to standard-cell eFPGA. Governments demand silicon sovereignty, automotive mandates zero-defect reliability, aerospace cannot tolerate external bitstreams or SEU-sensitive SRAM, industrial cannot tolerate cells not fully characterized for the expected temperature ranges, commercial cannot tolerate potential unexpected yield losses. Menta delivers the only eFPGA that meets all of those conditions natively — with ASIC-native power, timing, testability, and portability already built in.

- Fully portable across foundries and nodes

- Fully testable using standard ATPG and scan

- Fully compatible with aging, safety and yield flows

- Fully tunable per-customer for optimal PPA

- Zero hidden macros. Zero backdoors. Zero architectural lock-in.

This is not just reconfigurable logic.

This is reconfigurable trust — at ASIC speed, ASIC safety, and ASIC sovereignty.

And for System Architects and your fiscal bottom line, Menta’s eFPGA isn’t just a technology decision – it’s a lifecycle strategy.

| Goal | Menta Delivers |

| Accelerate Time-to-Market | Update hardware logic post-tapeout; Soft IP delivery in under 2 weeks with rapid ECO – change eFPGA IP definition up to the last minute! |

| Reduce Risk | Certifiable, testable, secure IP |

| Extend Product Lifespan | Reuse ASIC platforms across regions, generations |

| Ensure Sovereignty | No hard macro vendor lock-in |

| Lower Lifecycle Cost | Fewer SKUs, fewer respins, longer deployment horizon, higher yield and reliability |

In today’s semiconductor environment, agility without trust is a liability. The next generation of adaptive silicon must be flexible — but it must also remain verifiable, portable, and secure. If your eFPGA isn’t standard-cell, it’s not truly safe, certifiable, or sovereign. Menta proves that flexibility and trust can coexist — at ASIC scale.

About Menta

Menta, a pioneering leader in embedded FPGA (eFPGA) technology with over 15 years of proven success, delivers 100% standard-cell, third-party embedded FPGA IP for SoC, ASIC, and ASSP designs. As the only pure-play eFPGA provider offering silicon-proven, synthesis-free IP, Menta empowers semiconductor designers to adapt post-production — enabling rapid updates for bug fixes, customer-specific customizations, evolving standards, or enhanced security.

Our cutting-edge IP is delivered with the Origami toolchain, a seamless solution that generates bitstreams directly from RTL, streamlining design and accelerating time-to-market. Trusted by global semiconductor leaders, Menta transforms chips into agile, future-proof platforms — redefining what’s possible in silicon design. Want to learn more? Contact us at

Related Semiconductor IP

- eFPGA Soft IP

- eFPGA

- eFPGA on GlobalFoundries GF12LP

- Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

- Radiation-Hardened eFPGA

Related Blogs

- Design IP including Multi-standard SerDes enables risk-free, faster customer ASIC designs

- VIP Architecture: Why Native SystemVerilog and UVM?

- Why thinking about software and security is so important right at the start of an ASIC design

- Why AI Requires a New Chip Architecture

Latest Blogs

- Design specification: The cornerstone of an ASIC collaboration

- The importance of ADCs in low-power electrocardiography ASICs

- VESA Adaptive-Sync V2 Operation in DisplayPort VIP

- Design, Verification, and Software Development Decisions Require a Single Source of Truth

- CAVP-Validated Post-Quantum Cryptography