Tapeout Predictability with Hardened eFPGA IP Blocks

In the high-stakes world of modern SoC development, predictability is the ultimate currency. As design cycles shrink and the cost of a 5nm or 3nm mask set climbs into the tens of millions, the pressure to hit a tapeout date—and ensure first-pass silicon success—has never been higher.

For architects, adding flexibility via embedded FPGA (eFPGA) is a natural solution for post-silicon requirements, allowing for evolving standards and late-breaking feature additions. However, a critical question remains: Does adding programmable logic help your schedule, or does it introduce a new layer of uncertainty and risk? The answer lies in the delivery format. While soft IP offers configuration flexibility, hardened eFPGA IP blocks are the secret weapon for teams prioritizing tapeout predictability.

The “Soft” Problem: Complexity and Risk

Programmable logic reduces risk. However, using eFPGA through soft fabrics (RTL) places the burden of physical implementation squarely on the SoC team. Integrating a large block of programmable logic as RTL introduces significant hurdles:

- Physical Synthesis Hurdles: Managing timing closure for thousands to tens of thousands or hundreds of thousands of Look-Up Tables (LUTs) and complex routing matrices can derail a standard ASIC flow.

- Routing Congestion: eFPGA structures are inherently dense. Without expert-level floorplanning, you risk “unroutable” designs that only appear weeks before your deadline.

- Power Integrity: Predicting IR drop across a massive fabric of switches is a nightmare when the layout isn’t finalized until the end of the cycle.

If these issues arise at the 11th hour, your tapeout date becomes a mirage.

The Hardened Advantage: A “Known Good” Entity

A hardened eFPGA IP block takes a different approach. Instead of RTL, the fabric is provided as a fully characterized physical layout (GDSII). From the perspective of the SoC design team, the hardened eFPGA behaves like any other hardened IP block, similar to a high-speed SerDes or an SRAM macro.

- Guaranteed Timing and Power: With hard IP, timing models (lib files) and power profiles are characterized based on a finished layout. You aren’t guessing performance; the data is extracted from a silicon-ready design.

- Simplified Physical Integration: A hardened block comes with a fixed footprint and defined pin locations. Your back-end team simply “drops” the block into the floorplan. Internal routing resources do not interact with the rest of the chip’s routing, eliminating late-stage congestion surprises.

- Reduced Verification Scope: Instead of verifying a new fabric implementation, the SoC team integrates a pre-validated IP block. You only need to verify the interfaces, significantly reducing simulation and formal verification tasks.

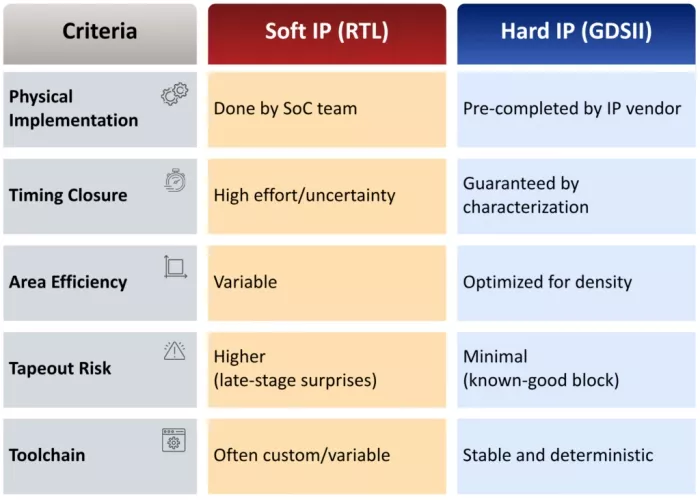

Comparison: Soft IP vs. Hard IP

Customization Without Compromising Schedule

One of the key advantages of our technology is the Australis eFPGA IP generator, which combines the predictable integration of hard eFPGA resources with the ability to deliver highly customized eFPGA IP. Unlike fixed arrays, we generate a hardened eFPGA optimized specifically for your application.

Engineers can tailor the architecture by selecting the exact number of LUTs, DSP blocks, and BRAM columns required. This ensures the fabric is not “overbuilt,” minimizing power consumption and silicon area. Furthermore, this IP can be targeted to nearly any process node or foundry, enabling architects to adopt eFPGA across advanced HPC nodes or mature industrial processes with equal confidence.

Predictable Tool Flows and Reproducibility

Predictability also extends to the FPGA User tools. With hardened eFPGA IP, the user tools are updated alongside the hardware to be process-node aware. This ensures stable synthesis, deterministic place-and-route algorithms, and version-controlled build environments. For long-lifecycle markets like aerospace or automotive, this reproducibility is vital for maintaining systems over decades.

Designing for Change Without Designing Risk

The irony of programmability is that it is often introduced to reduce risk, yet the wrong implementation model can create new uncertainties. Hardened eFPGA IP allows SoC teams to capture the benefits of flexibility—post-silicon updates and protocol adaptability—without turning the fabric into a source of design anxiety.

Architects gain a predictable hardware footprint, backend teams integrate a known macro, and project managers gain confidence in the schedule.

A Competitive Advantage

As mask costs climb, the cost of uncertainty grows exponentially. Companies that tape out reliably—without late surprises—gain a massive competitive advantage.

Hardened eFPGA technology provides a pragmatic solution for modern silicon design: flexibility where it matters, and predictability where it counts. It turns an experimental variable into a well-bounded, silicon-proven element of your SoC architecture.

Don’t let your programmable logic become a bottleneck. Choose the path of predictability.

Explore eFPGA IP:

Related Semiconductor IP

- Radiation-Hardened eFPGA

- eFPGA Hard IP Generator

- eFPGA on GlobalFoundries GF12LP

- eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

- Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

Related Blogs

- Synopsys Advances Die‑to‑Die Connectivity with 64G UCIe IP Tape‑Out

- Verifying CXL 3.1 Designs with Synopsys Verification IP

- Synopsys Secures Connected Vehicles with Industry's First IP Product to Achieve Third-Party Certification for ISO/SAE 21434 Cybersecurity Standard

- Trillions of Cycles per Day: How SiFive Boosts IP and Software Validation with Synopsys HAPS Prototyping System

Latest Blogs

- Considerations When Architecting Your Next SoC: NoCs with Arteris

- Implementing Dual-core Lockstep in the CHIPS Alliance VeeR EL2 RISC-V core for safety-critical applications

- Rethinking Display Safety: Why RISC-V-Supervised DisplayPort Subsystems Enable Secure, Isolated Automotive Architectures

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling