ReRAM in Automotive SoCs: When Every Nanosecond Counts

In automotive electronics timing is not just a performance preference. It is a safety requirement. Advanced driver assistance systems (ADAS) such as automated braking, lane keeping and emerging autonomy features all depend on fast, precise, deterministic behavior from the underlying silicon. When a system needs to react within microseconds, a handful of extra nanoseconds per instruction during a memory access can be the difference between life or death .

In automotive electronics timing is not just a performance preference. It is a safety requirement. Advanced driver assistance systems (ADAS) such as automated braking, lane keeping and emerging autonomy features all depend on fast, precise, deterministic behavior from the underlying silicon. When a system needs to react within microseconds, a handful of extra nanoseconds per instruction during a memory access can be the difference between life or death .

In this environment, average performance is not what matters. Only guaranteed performance matters. Automotive SoC designers must understand not only how fast memory accesses are on average, but also how slow they can possibly be. This is the fundamental reason that traditional memory hierarchies can introduce risk. They are optimized for throughput and averages, not hard real time determinism.

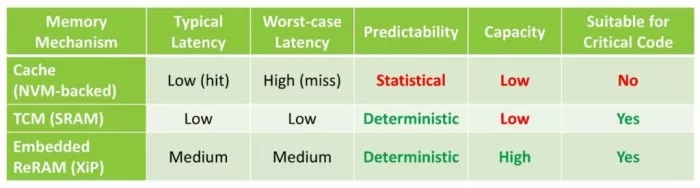

The Limits of Statistical Performance Mechanisms

Caches work beautifully in consumer and IoT devices. They enable fast access most of the time and they hide the latency of slower memory. But they also introduce uncertainty. A cache hit is fast. A cache miss is not. The problem is that hit rate is a statistical behavior. Even a system with a high hit rate can experience pathological miss patterns during a critical routine.

In a safety-critical automotive system, this variability is unacceptable. Engineers must calculate the worst-case execution time of every important code path. That calculation becomes significantly harder when instruction fetch cycles might be fast on one iteration and much slower on another. Branch predictors and speculative execution introduce similar unpredictability. They improve average performance but make timing analysis harder. For an ASIL* compliant design, unpredictability is the enemy.

The Role and Limits of Tightly Coupled Memories

To remove this uncertainty, SoC designers often turn to tightly coupled memories (TCMs). These memories sit next to the processor with a dedicated interface. This avoids contention on the system bus and provides guaranteed access timing. TCMs are a proven approach for real-time operation and are widely used in automotive microcontrollers.

However, the amount of software that now sits in the safety critical path has grown dramatically. ADAS and autonomous driving workloads increase the amount of code that must be treated as deterministic. Storing all that critical code in TCMs becomes difficult. In addition, TCMs are typically implemented using SRAM, which is relatively expensive in area and power. As the amount of required deterministic memory rises, designers start to feel architectural pressure. They need additional ways to host code that must meet strict timing constraints.

Why Executing from Embedded ReRAM/RRAM Changes the Equation

This is where the characteristics of embedded ReRAM (RRAM) become important. ReRAM delivers fast, consistent read latency without the multi-step read mechanisms used in flash. When flash is external, flash-based systems often require code to be shadowed into TCMs because direct execution from flash would be too slow or would introduce timing variability.

With ReRAM, it becomes practical to execute code directly from the non-volatile memory (NVM). This keeps the instruction fetch path consistent and predictable, which is essential for worst case timing analysis. It also reduces the hunger for large TCM blocks and lessens the reliance on cache behavior. If a routine can execute directly from ReRAM with constant latency, the system does not have to depend on statistical cache hit patterns to meet its timing budget.

This is particularly important as automotive systems move into advanced process nodes. Flash does not scale below 28 nanometers in an embedded form. That forces designers to use external flash, which introduces additional bus hops and more timing variation. ReRAM scales into these advanced nodes and offers deterministic behavior that is compatible with real-time execution.

System Level Benefits of Deterministic Embedded NVM

Deterministic access patterns simplify the certification process. When engineers know the exact memory latency of a code path, the analysis needed for ASIL compliance becomes more straightforward. The system-level architecture also becomes simpler. Designers can reduce the complexity of software placement rules, avoid special cache bypass strategies and remove a range of compensating mechanisms used to make flash-based systems behave in a deterministic way.

There are also power benefits. Shorter, more predictable instruction fetch cycles reduce switching activity across the memory hierarchy. This matters for always-on features and helps improve thermal behavior in compact automotive modules.

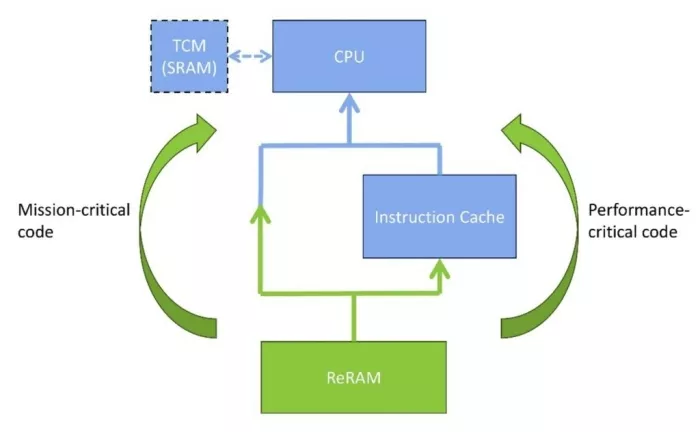

Today, the most effective designs use a hybrid memory strategy. Caches handle the non-critical parts of an application where peak performance matters more than strict determinism and smaller safety-critical routines can be placed in TCMs when needed. At the same time, larger critical code paths can run directly from on-chip ReRAM, which bypasses the cache entirely. This approach gives designers a strong balance of power efficiency, predictable timing and overall system performance.

Above: A hybrid approach partitions non-critical and critical parts of an application across memory resources for a strong balance of power efficiency, predictable timing and overall system performance

Explore ReRAM NVM IP:

Looking Ahead

Automotive SoCs will continue to evolve toward greater autonomy, higher sensor density and more compute-intensive algorithms. All these trends drive timing requirements in one direction. They become tighter every year. As workloads grow, designers cannot rely on probabilistic performance tools to keep systems safe. They need deterministic memory architectures that behave predictably under all conditions.

ReRAM provides this path. It is fast, consistent and scalable to the process nodes that the automotive industry is now adopting. When every nanosecond counts, the memory technology that underpins code execution becomes a foundational decision. ReRAM gives designers a reliable and deterministic platform for the next generation of automotive silicon.

Learn more about Weebit ReRAM in automotive applications by reading, The Road to AEC-Q100 Qualification.

*Automotive Safety Integrity Level (ASIL) is a risk classification scheme defined by the ISO 26262 standard.

Related Semiconductor IP

Related Blogs

- Arm and Arteris Drive Innovation in Automotive SoCs

- Design IP for Automotive SoCs: Trends and Solutions

- Synopsys 10BaseT1-S VIP for your Automotive SoCs

- 4 Critical Characteristics for Automotive SoCs