Epson Achieves 50% Energy Efficiency with QuickLogic eFPGA

First-Pass Success with QuickLogic eFPGA Hard IP on TSMC e12n

At QuickLogic, we pride ourselves on helping customers solve their toughest design challenges with flexible, efficient, and silicon-proven eFPGA Hard IP. Recently, one of our customers announced its achievement of a major milestone that illustrates some of the benefits of implementing QuickLogic eFPGA Hard IP in advanced SoC designs.

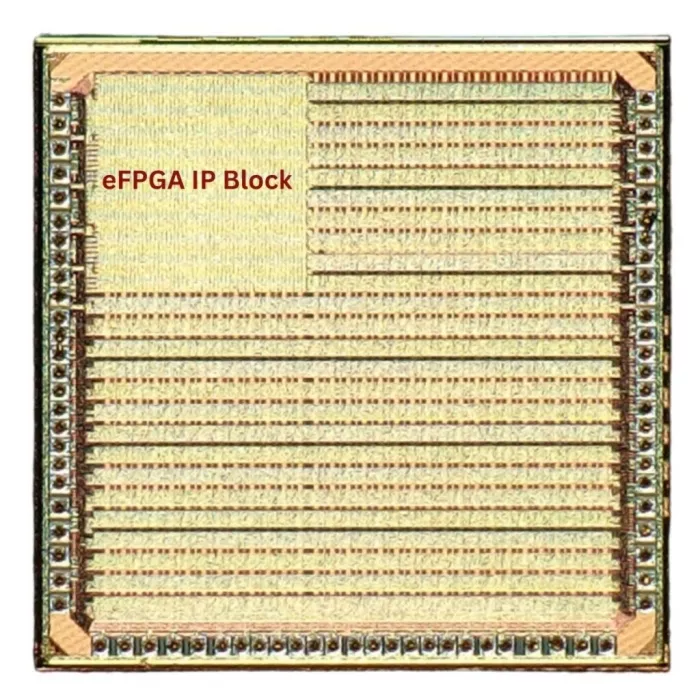

Epson’s design goals were to significantly reduce power consumption while improving performance and adhering to a tight schedule. By moving from a pure software implementation to QuickLogic’s eFPGA Hard IP, Epson achieved a 50% improvement in overall power efficiency while maintaining the programmability needed to adapt to evolving algorithms and market requirements. Leveraging over 30 years of experience and its proprietary Australis Hard IP Generation Tool, QuickLogic delivered customer-specific Hard IP for TSMC’s e12n fabrication process that met Epson’s specifications in the first silicon pass.

Epson’s design goals were to significantly reduce power consumption while improving performance and adhering to a tight schedule. By moving from a pure software implementation to QuickLogic’s eFPGA Hard IP, Epson achieved a 50% improvement in overall power efficiency while maintaining the programmability needed to adapt to evolving algorithms and market requirements. Leveraging over 30 years of experience and its proprietary Australis Hard IP Generation Tool, QuickLogic delivered customer-specific Hard IP for TSMC’s e12n fabrication process that met Epson’s specifications in the first silicon pass.

According to Maho Terashima, Director of Device Technology Development at Epson, this achievement was made possible through the combination of Epson’s low-power circuit design expertise and QuickLogic’s eFPGA technology.

Epson operates in a market where energy efficiency is paramount and increasing battery capacity is not an option. Their system was originally architected to run workloads entirely in software, but as demand for more features and real-time responsiveness grew, power consumption became a limiting factor. The engineering team recognized that moving compute-intensive functions into dedicated hardware could deliver significant efficiency gains — but only if the hardware could continue to adapt to evolving algorithms and changing market requirements.

With these challenging requirements, the engineers determined that by embedding an FPGA (eFPGA) fabric directly into their SoC they could accelerate key algorithms in hardware while retaining the adaptability of a software-driven system and, in doing so, significantly lowering power consumption and improving performance.

Optimized for Low Power on TSMC e12n

Working closely with QuickLogic’s team, Epson selected an Australis-generated eFPGA Hard IP core optimized specifically for TSMC’s e12n low-power process. This combination was ideal:

- TSMC e12n technology provided a baseline of excellent transistor performance with industry-leading low leakage characteristics optimized for low power consumption.

- QuickLogic’s proprietary eFPGA IP generator (Australis) allowed the architecture — LUT count, Block RAM and interconnect to be tailored to the workload.

- Low-power optimizations were applied throughout, including clock gating and fine-tuned routing resources to minimize dynamic switching.

The result was a right-sized fabric that avoided unnecessary overhead while delivering ample performance headroom in the first pass.

First-Pass Silicon Success

From design handoff to silicon validation, the IP integrated cleanly into Epson’s SoC without the need for re-spins or late-stage design changes. Epson was able to boot, configure, and validate the eFPGA subsystem immediately, accelerating its schedule and reducing risk.

Explore eFPGA IP:

Measurable Efficiency Gains

When the system was benchmarked, the results were clear. By migrating selected software routines into the eFPGA fabric, Epson achieved a 50% improvement in overall energy efficiency. This not only extended battery life for their application but also enabled higher performance modes without exceeding thermal or energy budgets.

Broader Implications

This project illustrates why more and more SoC developers are turning to embedded FPGA IP:

- Flexibility — eFPGA enables hardware to provide the flexibility of software

- Efficiency — significant power and performance improvements versus running everything in software

- Confidence — silicon-proven Hard IP with demonstrated first-pass success

For QuickLogic, it reinforces our commitment to delivering optimized, low-power, and customizable eFPGA IP solutions for a wide range of markets, from consumer to industrial to defense.

Conclusion

Epson’s achievement is a strong validation of QuickLogic’s eFPGA technology on advanced low-power processes like TSMC e12n. By combining software-defined adaptability with hardware-level efficiency, Epson was able to deliver its system on schedule, while also making it more capable and more energy-efficient.

We look forward to enabling more customers to achieve similar success as they bring innovative products to market.

Related Semiconductor IP

- Radiation-Hardened eFPGA

- eFPGA Hard IP Generator

- eFPGA on GlobalFoundries GF12LP

- eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

- Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

Related Blogs

- ASICS versus FPGAs versus ASICs with eFPGA Technology

- Why is Hard IP a Better Solution for Embedded FPGA (eFPGA) Technology?

- Bringing Silicon Agility to Life with eFPGA and Intel’s 18A Technology

- Smarter ASICs and SoCs: Unlocking Real-World Connectivity with eFPGA and Data Converters

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk