One Bit Error is Not Like Another: Understanding Failure Mechanisms in NVM

When talking about memory reliability, the discussion often converges into a single question: how many errors occur over time? But that question misses something critical. In Non-volatile memory (NVM), how errors occur is just as important as how often they occur.

All non-volatile memory (NVM) devices, including flash, ReRAM, and others, experience failure mechanisms driven by device physics and typical usage. But the failure mechanisms are different between the various NVM technologies, leading to very different system-level behaviors, design trade-offs, and qualification strategies.

This distinction becomes especially important when comparing conventional flash memory with emerging technologies such as Resistive RAM (ReRAM or RRAM). While both are non-volatile, the physics that govern how they store data, and how they fail, are fundamentally different. Flash failures are more dominated by hard failure mechanisms, while ReRAM faces more stochastic* variability.

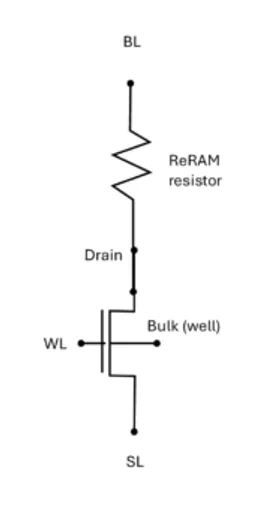

Above: The 1T1R structure of ReRAM. Each memory cell consists of a resistive switching element (1R) in series with a select transistor (1T)

Understanding these different failure mechanisms is crucial for improving reliability, extending lifespan, optimizing performance, and ensuring data integrity over a product’s lifetime.

Flash Memory: Wear-Driven, Cumulative Failure

Flash memory stores information by trapping charge in a floating gate or charge-trap layer. Over time, repeated program/erase cycles gradually degrade the insulating oxide layer, leading to well-understood wear-out mechanisms. As oxide damage accumulates, leakage increases, and cells gradually lose their ability to reliably store charge.

In addition, repeated access to nearby cells can introduce disturb effects, where programming or reading one cell subtly alters the charge state of another. These mechanisms are strongly cumulative: once a cell begins to fail, it typically continues to degrade. Errors observed late in a flash device’s lifetime are therefore a strong indicator of permanent damage rather than transient behavior. As a result, flash reliability models are built around tracking wear accumulation and predicting end-of-life behavior.

ReRAM: Stochastic Behavior Rooted in Device Physics

Like flash, ReRAM experiences reliability failures from endurance and retention loss, but it is less prone to disturb effects due to the select transistor blocking current in unselected cells. However, variability is more critical in ReRAM because of stochastic filament behavior, which is moderate in mature flash. ReRAM is also more robust against radiation than floating gate flash.

ReRAM stores data in a completely different way than flash. ReRAM stores data by forming and breaking conductive filaments inside a resistive switching layer. Importantly, filament formation is governed by probabilistic laws controlling the generation, motion, and recombination of oxygen vacancies in the resistive layer. This leads to inherent cycle-to-cycle variability: even under identical operating conditions, the exact shape, size, and conductivity of a filament can vary from one programming cycle to the next.

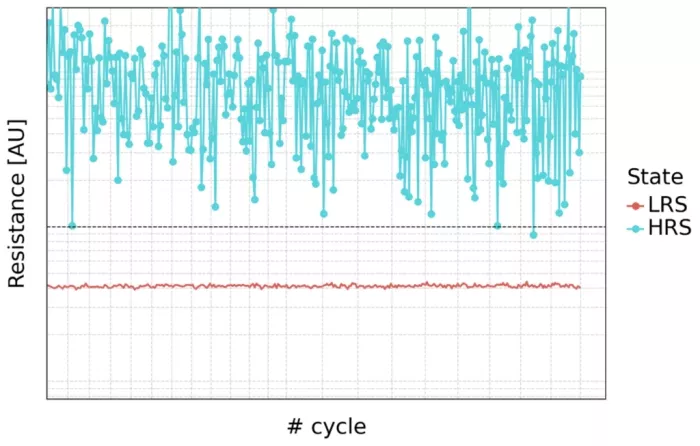

Above: Cycling characteristics of a ReRAM cell, illustrating the stochastic character of the observed error

This leads to fluctuations in resistance each time the cell is written. Errors are typically not cell-related (i.e., not due to a permanently broken cell) but cycle-related. A cell can fail in one programming cycle and recover in the next due to the stochastic nature of filament formation.

This distinction is critical. The variability-driven errors of ReRAM are intermittent and non-persistent, fundamentally different from the irreversible wear-out-driven failures of flash.

Why Flash Assumptions Break Down for ReRAM

Historically, NVM qualification has been built around flash behavior. Designers assume the memory array must be nearly error-free on its own, treat errors as signs of degradation, and reserve guard bands for unexpected failures late in life.

ReRAM does not fit this model cleanly. Because variability-driven errors are a normal part of operation, raw error counts alone are a poor indicator of aging or failure. Interpreting ReRAM behavior through a flash-centric lens can lead to overly conservative designs, unnecessary performance penalties, or misleading reliability conclusions.

More broadly, it obscures a real advantage of ReRAM: its robustness against cumulative wear and its ability to operate reliably even in the presence of statistical variation.

Designing with Physics in Mind

The growing maturity of ReRAM is enabling broader adoption in storage and computing applications, with reliability playing a central role in this progress.

But reliability is not just about minimizing errors; it’s about understanding what those errors mean. Flash and ReRAM fail differently because their underlying physics are different. In flash, an error often signals irreversible aging, while an error in ReRAM may simply reflect statistical variation in a perfectly healthy device. Treating these two behaviors as equivalent leads to incorrect conclusions about device health and lifetime.

With this understanding, designers can create better mitigation strategies, predict device failure, and create more efficient algorithms. Systems with ReRAM can be more intelligently designed for their lifetime, without over-engineering. As we move beyond the flash for many applications, designing with the physics, rather than against it, is what will ultimately unlock the full potential of next-generation NVM.

* ‘Stochastic’ is defined as having a random probability distribution or pattern that may be analyzed statistically but may not be predicted precisely.

Related Semiconductor IP

Related Blogs

- Bit Error Rates for USB 3.2

- Synopsys acquires Magma! And, another one bites the dust!!

- Apple Will NOT Buy ARM

- Electronic Design Automation (EDA): Failure of Capitalism?

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk