Introducing the Akeana 1000 Series Processors

Akeana was founded with the mission of delivering maximum performance and advanced capabilities to the RISC-V ecosystem.

The core team behind Akeana has worked together for decades, leveraging their deep expertise to shape the company and develop a distinctive design approach. This methodology enables rapid integration of new features into processor cores, allowing tailored configurations optimized for specific use cases.

With extensive experience in data center-grade processors, the Akeana team delivers industry-leading performance. This empowers customers to future-proof their designs with top-tier processing power—or reduce silicon real estate without compromising on performance.

A few weeks ago, we presented to you the Akeana 5000 Series Processors, Akeana’s Top Performance Series that exceeds 25 SpecInt2K6 per GHz – a performance leader in the RISC-V IP Market!

Today we present to you the Akeana 1000 Series Processors, a series of High Performance processors IP which is optimized for AI applications and workloads, thus providing a quick AND efficient processing solution for your AI needs.

The Akeana 1000 Series of processors is highly configurable and customizable, supporting applications from smart homes and wearables, to automotive ADAS applications. These processors can be configured with support for 1-, 2-, or 4-way Multi-threading.

A popular use case for this family of cores is as control processors and vector extension engine (for activations) in the AI use cases specifically, and more generally in SoCs where these cores integrate with a customer’s own accelerators.

The Akeana 1000 Series is optimized for a broad range of applications, available with either an In-Order or Out-of-Order microarchitecture and from single-issue to quad-issue instruction issue width, to provide customers with the range needed for a variety of computation requirements.

- 9-stage in-order or 12-stage out-of-order pipeline

- Multithreaded (SMT) architecture support.

- MMU with up to 512 entries, 4-way TLB.

- Up to 4-wide issue architecture.

The Akeana 1000 Series is the midrange of Akeana’s three processor product lines, offering customers one of the broadest available processor IP portfolios. Start your journey today with one or more of these Akeana processors.

Standard Configurations vs Tailored Configurations:

At Akeana, we offer a very wide portfolio of cores with a uniquely simple approach for your choice:

- Choose one of our 10 baseline processors as the closest to your system requirements. This is typically done based on the core’s ‘hard’ features such as pipeline architecture and performance work-point.

- Tailor the core’s features to make it ideal for your core requirements.

Thus, with a simple set of 10 baseline cores in three different performance levels, you may create a custom configuration that is ideal for your SoC.

Akeana 1000 Series Standard Configurations

Akeana 1000 Series Add-On Options

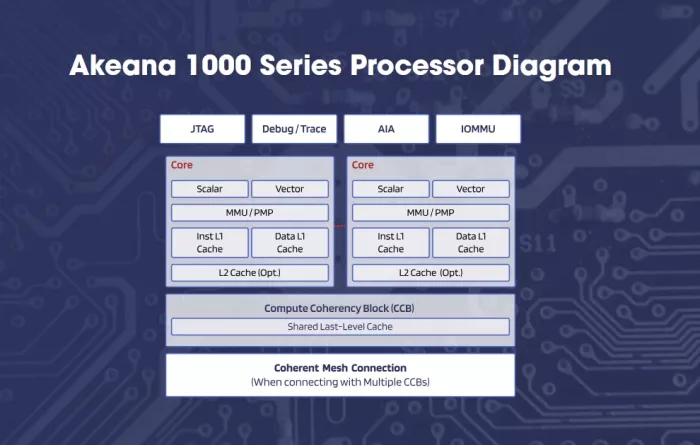

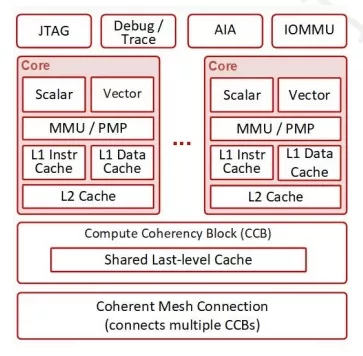

Multi-Core Coherency Cluster:

All Akeana 1000 Series processors can extend performance with multi-core configurability, up to 8-cores in a single coherent cluster. A multi-core coherent cluster includes a CCB (Compute Coherence Block), which manages coherency across both the multi-core cluster and external accesses. The CCB also includes a Shared Cache block.

Many-cluster coherent CPU Subsystems are also fully supported. Heterogeneous Clusters – including different Akeana cores – are also fully supported.

Advanced Memory and Caching Architecture:

The Akeana 1000 processor in a single-core configuration has 2 levels of private Caching for Data Memory. The L1 Data Cache is configurable up to 64KB. Instructions are cached in a L1 Instruction Cache, configurable up to 128KB. The L2 Cache is unified (caches both Instructions and Data). It is configurable up to 1MB in size and available with up to 16-way associativity. In configurations with no L2 Cache, there is an

external interface for Instruction loads. For Multicore configurations, a shared Level 3 Cache (L3C) is available, located in the CCB, and configurable up to 16MB in size.

The Akeana 1000 cores provide Physical Memory Protection (PMP), which provides access privilege control for ranges of physical addresses. PMP can be configured with up to 64 entries.

Linux OS support with MMU:

The Akeana 1000 cores includes an MMU with Translation Look-aside Buffer (TLB) to support virtual memory operations. The MMU is configurable up to 2048- entry, 8-way TLB.

Vector Extension:

The Akeana 1000 family supports the option of adding RISCV Vector Extension v1.0. The Vector pipeline runs in parallel to the Scalar pipeline, with In-Order execution. VLEN (vector register width) is equal to DLEN (datapath width) and both are configurable up to 4096 bits wide. LMUL operations (with LMUL from 1/8 to 8) are fully supported. Vector Load and Stores have their own dedicated pipeline and access memory through the L1 data cache.

Security and RAS features:

- TrustZone™ Capability: Akeana processors implement security features required by Arm’s TrustZone, hence TrustZone software can be easily ported to work with Akeana processors. However, Akeana’s processors support a larger number of distinct Secure and Non-Secure zones (security domains).

- Security Monitors, Telemetry: An Akeana 1000 core provides multiple Performance and Security monitors. Those monitors provide detailed core behavior information which, through an external interface, can be used to monitor performance and power profiles. They can also provide visibility into possible security attacks, by detecting and flagging malicious activity signatures.

- Vector Performance: An Akeana 1000 core includes a RISC-V Vector (v1.0) execution unit. The vector unit is fully integrated, executing in parallel with other pipelines. A full range of vector datatypes (INT, FP, and BF16) is supported, as well as vector cryptographic extensions. The vector length can be configured with up to 4096-bit VLEN and DLEN.

External Interfaces:

- Data Load and Store: AXI, ACE or CHI Master

- Instruction Fetch: AXI Master

- Optional System Bus/Debug: AXI Master

- Power Management (PMU) interface

- Optional DMA AXI Slave

- Optional Telemetry Interface

Flexible Clocking, DVFS:

The processor core can operate at a different clock frequency than the CCB block and its external interfaces. The clocking ratios can be either synchronous or asynchronous.

Per-core DVFS is supported with asynchronous clocking and physical implementation of voltage isolation measures.

Interrupt Controllers:

Akeana offers a companion Advanced Core-Level Interrupt Controller (CLINT) and a Platform-Level Interrupt Controller (PLIC), as separate deliverable IP blocks. These interrupt controllers are configurable to customer requirements and are fully compliant with RISC-V specifications.

Debug and Trace:

The Akeana 1000 processor family conforms to the RISC-V External Debug Support, Version 0.13.2 specification with the JTAG Debug Transport Module (DTM). Debug features include Abstract Command, System Bus Access, and Triggers. There is an optional Multi-processor Controller (MPC) Debug Interface.

The Akeana 1000 cores provide a Trace interface that conforms to the Efficient Trace for RISC-V, Version 2.0.1 and RISC-V Trace Control Interface specification, Version 1.0.0 specifications.

Akeana IP Configurability:

The Akeana 1000 processor cores, like all Akeana processors, are configurable to customer specifications. Customers can select options to meet their specific needs. This configurability extends across all processors, memory system, Interrupt Controllers and Network-on-Chip IP blocks from Akeana.

Broadest Range of Evaluation Platforms:

Akeana provides support for multiple evaluation and emulation platforms. This allows customers working with anything from small single core solutions to very large, fully coherent multi-core solutions to run emulation at high speed for hardware and software development, using tools such as:

- Xilinx VCU118 FPGA board

- The Veloce proFPGA platform

- Synopsys HAPS-100 prototyping system

- Cadence Palladium emulation platform

Advanced Software Development Capabilities:

Akeana processors are supported by a variety of third-party IDE and Debugging tools, including:

- Ashling’s RiscFree™ Integrated Development Environment (IDE) and Debugger for RISC-V.

- OpenOCD (Open On-Chip Debugger), opensource software that interfaces with a hardware debugger’s JTAG port.

Akeana 1200 – the Flagship In-Order 1000 Series Standard Configuration:

The Akeana 1200 is a 64-bit RISC-V processor, featuring In-Order execution with 3-way instruction dispatch. It implements the full RISC-V RVA22 or RVA23 Processor Profile and can support rich operating system environments (such as Linux or Android). The Akeana 1200 is highly configurable and customizable, enabling customers to define the processor to meet their computation requirements.

The Akeana 1200 Key Features:

- 64-bit RISC-V ISA , supporting RVA23 Profile

- 3-way instruction dispatch , 9-stage, in-order application processor

- Full Scalar data types supported (integer and floating point)

- L1 and L2 Caching (optional)

- Option to add RISC-V Vector Extension (v1.0) with up to 4096-bit VLEN (register), 4096-bit DLEN (datapath), and 9-stage Vector execution pipeline

- Physical addressing: 39 bits (opt: 32)

- Virtual addressing: 39 bits (opt: 48 or 57 bits)

- Physical Memory Protection (PMP): 16 entries (option: up to 64)

- MMU support, with 512-entry, 4-way TLB (opt: up to a 2048-entry, 8-way TLB)

- Option for Multi-Threading, up to 4-way

- Advanced Power Management features with PMU interface

- Up to 8 cores in Multi-core/single-cluster configuration. Includes a Coherent Cluster Block (CCB) for Coherency management

- Advanced Interrupt Architecture (AIA), including blocks ACLINT and APLIC

- Akeana IOMMU IP

- Akeana NCI (Non-Coherent IP) blocks, conforming to AMBA AXI NoC

- Akeana Mesh: Coherent NoC IP blocks, conforming to AMBA CHI protocol. A coherent 2D Mesh array of any size can be created.

- TrustZone security support

- Security and Telemetry features, for detecting malicious activity signatures

Related Semiconductor IP

- Specialized Video Processing NPU IP for SR, NR, Demosaic, AI ISP, Object Detection, Semantic Segmentation

- LLM AI IP Core

- RISC-V-Based, Open Source AI Accelerator for the Edge

- RISC-V AI Acceleration Platform - Scalable, standards-aligned soft chiplet IP

- CNN AI IP Core

Related Blogs

- What will it take for FPGAs to become as ubiquitous as processors?

- How many people does it take to design an SoC? - Redux. Building brains with processors.

- Microprocessor Report publishes extremely interesting comparison of STMicroelectronics SPEAr-1300 and Xilinx Zynq ARM-based, dual core application processors

- Will AMD Make ARM Processors?

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk