High-speed IP

Welcome to the ultimate High-speed IP hub! Explore our vast directory of High-speed IP

All offers in

High-speed IP

Filter

Compare

217

High-speed IP

from

35

vendors

(1

-

10)

-

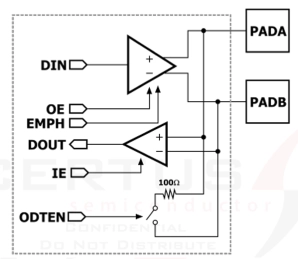

Rad-Hard GPIO, ODIO & LVDS in SkyWater 90nm

- This Library, developed on SkyWater 90nm CMOS, delivers a radiation-hardened suite of robust interfaces covering general-purpose, open-drain, and high-speed differential signaling needs.

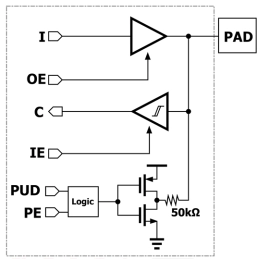

- The GPIO provides reliable 3.3V digital I/O up to 150 MHz with JESD8C.01 compliance, built-in pull-ups/downs, and 2 kV HBM protection.

-

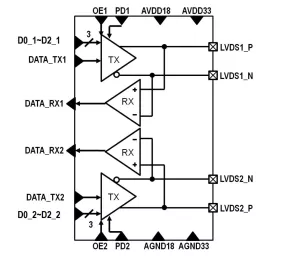

LVDS IO handling data rate up to 50Mbps with maximum loading 60pF

- KA16UGLVDS01ST001 is a LVDS IO handling data rate up to 50Mbps with a maximum loading of 60pF.

- The differential voltage swing can be programmable from 0.35V to 1V.

- The output enable control function can be activated to decide the IO as input/output function. This IP also includes the IO PAD.

-

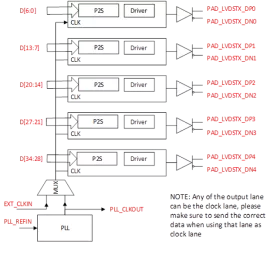

LVDS and OpenLDI PHY

- Silicon proven with maximum speed @1.5Gbps per lane

- Suitable for Automotive applications with ESD levels: HBM > 4KV and CDM > 750V

- LVDS TX PHY: 4-data lanes plus 1-clock lane with each lane can be individually turned off

- Supports long-distance transmission: Capable of maintaining signal integrity over longer cable length

-

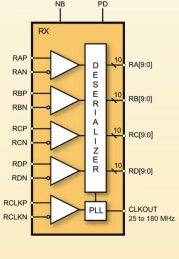

LVDS Deserializer IP

- The MXL-DS-LVDS is a high performance 4-channel LVDS Deserializer implemented using digital CMOS technology.

- Both the serial and parallel data are organized into four channels. The parallel data can be 7 or 10 bits wide per channel. The input clock is 25MHz to 165MHz. The De-serializer is highly integrated and requires no external components.

-

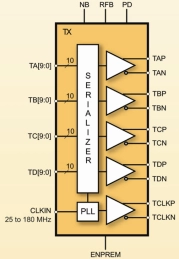

LVDS Serializer IP

- The MXL-SR-LVDS is a high performance 4-channel LVDS Serializer implemented using digital CMOS technology. Both the serial and parallel data are organized into four channels.

- The parallel data width is programmable, and the input clock is 25MHz to 165MHz. The Serializer is highly integrated and requires no external components.

-

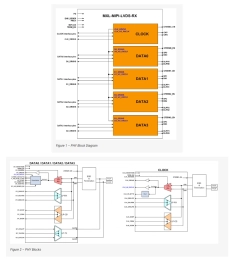

MIPI D-PHY/LVDS Combo Receiver IP

- The MXL-LVDS-MIPI-RX is a high-frequency, low-power, low-cost, source-synchronous, Physical Layer that supports the MIPI® Alliance Standard for D-PHY and compatible with the TIA/EIA-644 LVDS standard.

- The IP is configured as a MIPI slave and consists of 5 lanes: 1 Clock lane and 4 data lanes, which make it suitable for display serial interface applications (DSI).

-

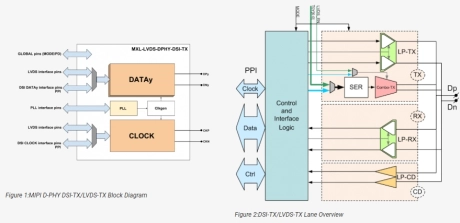

MIPI D-PHY/LVDS Combo Transmitter IP

- The MXL-LVDS-DPHY-DSI-TX is a combo PHY that consists of a high-frequency low-power, low-cost, source-synchronous, Physical Layer supporting the MIPI® Alliance Standard for D-PHY and a high performance 4-channel LVDS Serializer implemented using digital CMOS technology.

- In LVDS mode, both the serial and parallel data are organized into 4 channels. The parallel data is 7 bits wide per channel. The input clock is 25MHz to 150MHz. The serializer is highly integrated and requires no external components. The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

-

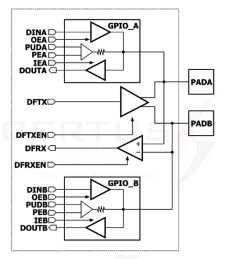

Ultra-low leakage I/O Library in TSMC 22nm

- A TSMC 22nm Wirebond I/O Library with ultra-low leakage 1.8V GPIO, 1.8V I2C ODIO, 1.8V analog cell and associated ESD.

- This is an ultra-low leakage library. The GPIO has a typical leakage of only 150pA from VDDIO and 1nA from VDD.

- The library has a GPIO and an ODIO. The GPIO cell set can be configured as input or output and has an internal 50K ohm pull-up or pull-down resistor.

-

2Gbps LVDS/SVLS Combo Transceiver in TSMC 16nm

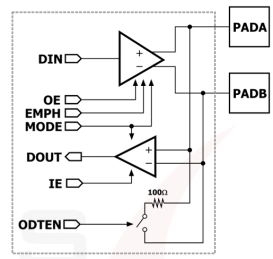

- AD_SLVS_LVDS is a highly configurable 2Gbps transceiver for LVDS or SLVS interfaces. With features like dynamic interface selection, on-die termination and pre-emphasis, this I/O is flexible enough for any system.

- To compliment this I/O, the vendor also offers a accompanying silicon-proven ESD and GPIO pad library in TSMC 12/16nm.

- This I/O provides 2kV HBM protection but can be extended up to 8kV upon request.

-

LVDS Transceiver in TSMC 28nm

- This 1.8V LVDS transceiver, designed for TSMCs 28nm process, delivers high-speed, low-power differential signaling with superior signal integrity.

- Engineered with 1.8V thick oxide devices and a 0.8V standard core interface, it operates ef- ficiently across a wide temperature range (-40°C to 125°C).