subLVDS IP

Welcome to the ultimate subLVDS IP hub! Explore our vast directory of subLVDS IP

All offers in

subLVDS IP

Filter

Compare

33

subLVDS IP

from

5

vendors

(1

-

10)

-

Library of LVDS IOs cells for TSMC 65LP

- TSMC 65 LP

- 2.5V/1.2V IO/Core transistors

- Fully compliant with TIA/EIA-644-A-2001

-

Library of LVDS IOs cells for TSMC 40LP

- TSMC 40 LP

- 2.5V/1.1V IO/Core transistors

- Fully compliant with TIA/EIA-644-A-2001

-

Sub-LVDS receiver followed by 1:4 de-serializer

- Sub-low voltage differential signaling input: VID = 25mV MIN.

- Converts the subLVDS strobe/data (up to 960 Mbps throughput bandwidth) back into parallel 4 bits of CMOS data/strobe

- Power-down control function

- Full industrial operating temperature range -40 ~ +125 °C

-

Camera Combo Receiver - 2.4Gbps 8-Lane - TSMC 28nm HPC

- The CL12832M8R2JM3KIP2400 is designed to support data rate in excess of maximum 2.4Gbps utilizing SLVS-EC / sub-LVDS / CMOS 1.8V interface specification.

- The CL12832M8R2JM3KIP2400 can change Interface type to same PAD for changing mode.

-

Camera Combo Receiver - 1.5Gbps - 4-Lane - TSMC 40LP

- The CL12662K4R1AM2JIP1500 is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to ISP (Imaging Signal Processer) and DSP.

- The CL12662K4R1AM2JIP1500 is designed to support data rate in excess of maximum 1.5Gbps utilizing sub-LVDS / MIPI D-PHY v1-1 interface specification.

- The CL12662K4R1AM2JIP1500 can change Interface type to same PAD for changing mode.

-

MIPI D-PHY/sub-LVDS combo Transmitter - 4-Lane, 1.5G/1.0Gbps - TSMC 40LP

- The CL12661K4T1AM2JIP is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to Host System.

- The CL12661K4T1AM2JIP is designed to support data rate in excess of maximum 1.5Gbps utilizing sub-LVDS / MIPI-DPHY interface specification.

- The CL12661K4T1AM2JIP can change Interface type to same PAD for changing mode.

-

SMIC 55nm sub-LVDS Receiver

- Supports Aptina HiSPi, Panasonic LVDS, or Sony LVDS parallel input signal

- 8 data channels / 2 clock channel integrated

- Maximum serial data rate per channel: 1Gbps

- Supports up to 16-bit CMOS parallel input (DVP input mode)

-

SMIC 55nm sub-LVDS Receiver

- Supports Aptina HiSPi, Panasonic LVDS, or Sony LVDS parallel input signal

- 10 data channels / 2 clock channel integrated

- Maximum serial data rate per channel: 1Gbps

- Supports up to 20-bit CMOS parallel input (DVP input mode)

-

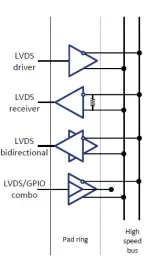

subLVDS IO Pad Set

- ? Powered from 1.8V ±10% and 1.1V to 1.2V (±10%) core power supplies

- ? Operates up to 700 MHz (1400Mbps)

- ? Input receive sensitivity of 50mV peak differential (without hysteresis)

- ? Common mode range from 0.4V to 1.4V (limited by Power Supply)

-

GLOBALFOUNDRIES 28nm SLP 1.8v/1.0v SUBLVDSTX

- Process: GF 28nm SLP 1.0V/1.8V CMOS process

- Supply voltage: 1.62V<=AV18_TX(AVDD)<=1.98V,0.9V<=AVDD2(DV10)<=1.1

- Mos device type: egpfet, egnfet, pfet, nfet

- Operating junction temperature: - 40°C ~ +25°C ~ +125°C