LPDDR5 IP

Welcome to the ultimate LPDDR5 IP hub! Explore our vast directory of LPDDR5 IP

All offers in

LPDDR5 IP

Filter

Compare

107

LPDDR5 IP

from

16

vendors

(1

-

10)

-

LPDDR5X/5/4X/4 combo PHY at 7nm

- Compliant with JEDEC JESD209-5B for LPDDR5X/5/4X/4 with PHY standards

- Delivering up to 8533Mbps

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

-

LPDDR5X/5/4X/4 combo PHY at Samsung SF5A

- Compliant for JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

- x16 and x32 channel support

-

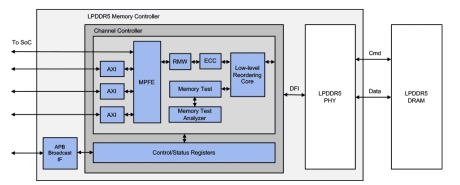

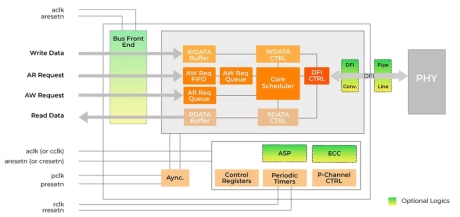

LPDDR6/5X/5 Controller IP

- Supports JEDEC standard LPDDR6, LPDDR5X and LPDDR5 SDRAMs

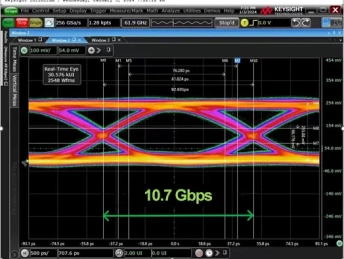

- Support for data rates up to 14.4 Gbps for LPDDR6, 10.67 Gbps for LPDDR5X, and 6.4 Gbps for LPDDR5

- Multiport Arm® AMBA® interface AXI™4 with managed QoS or single-port host interface to the DDR controller

- DFI 5.2 compliant interface to Synopsys LPDDR6/5X/5 PHY

-

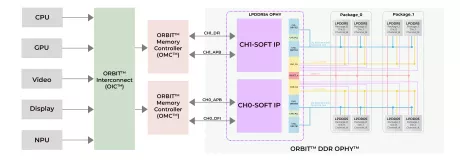

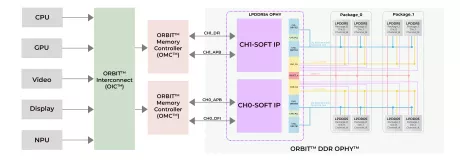

LPDDR5X/5/4X/4 PHY & Controller

- The LPDDR IP includes a LPDDR5X/5/4X/4 Combo PHY and controller.

- It is fully compliant with the JEDEC standard. Optimized for low-power and high-speed applications, it ensures robust timing and a small silicon area.

- The PHY IP contains specialized functions to guarantee high-performance I/Os, critical timing, low power and jitter with programmable fine-grain control for any SDRAM interface.

-

LPDDR5X/5/4X/4 combo PHY at 12nm

- Compliant with JEDEC JESD209-5C for LPDDR5x/5/4x/4 with PHY standards

- Delivering up to 8533Mbps

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

- Multiple frequency states

-

LPDDR5X/5/4X/4 PHY for 16nm

- Compliant with JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports up to 4 ranks

- Multiple frequency states

-

LPDDR5/4x/4 combo PHY on 14nm, 12nm

- Compliant with JEDEC standards for LPDDR5/4x/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports 1,2, or 4 ranks

- Multiple frequency states

-

LPDDR5/4x/4 PHY IP for Samsung 14LPU

- Compliant with JEDEC standards for LPDDR5/4x/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports 1,2, or 4 ranks

- Multiple frequency states

-

-

LPDDR5T / LPDDR5X / LPDDR5 Controller

- Support for all LPDDR5T/5X/5 devices

- Bank management logic monitors status of each bank

- Queue-based user interface with reordering scheduler

- Look-ahead activate, precharge, and auto-precharge logic

- Parity protection for all stored control registers

- PHY interface based on DFI 5.1 standard