Memory Controller

Delivers excellent performance in addition to high utilization and ultra-low latency, achieved by its proprietary out-of-scheduli…

Overview

Delivers excellent performance in addition to high utilization and ultra-low latency, achieved by its proprietary out-of-scheduling algorithm and high-speed implementation. Designed to address the needs of next-generation SoCs, the OMC saves a significant amount of area and power while supporting the highest levels of the DRAM bandwidth.

| DDR Type | Target Applications |

| GDDR6 | HPC (Al/ML), Edge PC, Data Center, Server, PC, Coin |

| LPDDR4 | Mobile, Automotive, loT, Broadcasting |

| LPDDR4X/3 Controller | Mobile, Automotive, loT, Surveillance, STB, DTV, SSD |

| LPDDR5X/5/4X Controller | Automotive, HPC (Al/ML), Broadcasting |

| DDR4/3 Controller | STB, DTV, SSD, Network, Surveillance |

| HBM3 Controller | HPC (Al/ML), Coin, Data Center |

Key features

- DRAM Support

- JEDEC compliant LPDDR5x/5/4x/4/3, DDR4/3, GDDR6, HBM3 support

- Up to 4 ranks/channel (configurable)

- High Performance

- A proprietary out-of-order scheduling algorithm

- Dual-PHY control for 2x DRAM channel bandwidth with a single OMC instance

- Low Power Consumption

- Ultra-low power consumption with HW-controlled dynamic DRAM frequency scaling

- Automatically handles training activities required for frequency change

- Automated DRAM power management

- Special Features

- BFE (Bus Front End) for multi-master ports (optional)

- Configurable Options

- DRAM types (LPDDR5x/5, DDR4, LPDDR4x/4, DDR3/LPDDR3, GDDR6)

- Channel DQ width (x16, x32, x64)

- Number of AXI master ports (up to 8)

- AXI master data width and frequency

- Request queue depth

- Write and read data queue depth

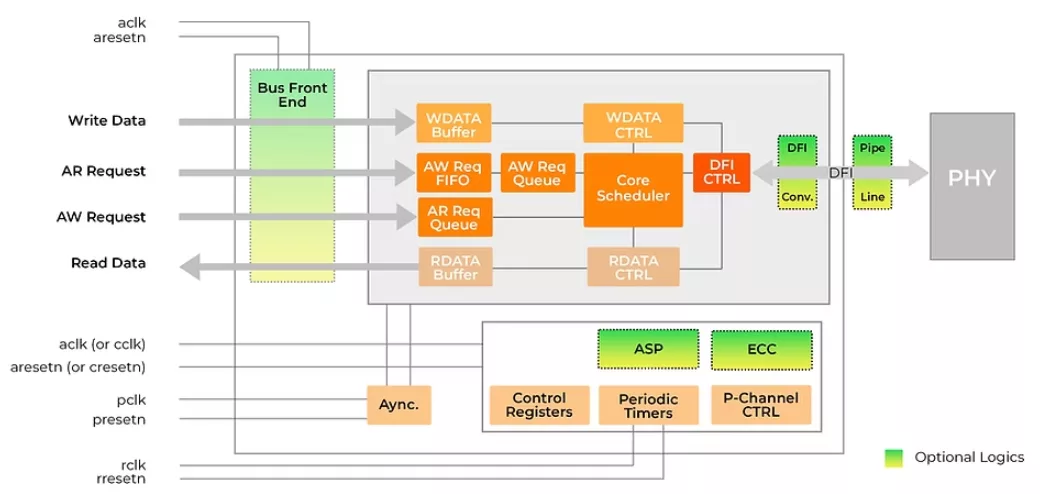

Block Diagram

Benefits

- Intensive DRAM Utilization

- Over 90% DRAM utilization using a proprietary out-of-order scheduling algorithm

- Optimal pipeline architecture

- Ultra-Low Power Consumption

- Hardware-controlled dynamic DRAM frequency scaling

- Automates training activities required for frequent changes

- Highly area-efficient

- Extremely Low Latency

- Low latency even in high utilization scenarios

- Suppression of peak latency using the latency-aware algorithms

- Safety & Security

- Inline ECC

- Security Firewall

Applications

- Automotive

- Application Processors

- HPC/Super Computing

- Block Chain/Crypto Currency

- Digital TV

- Data Center

- Game Console

- Entertainment

- Graphic Cards

What’s Included?

- OMC is packaged with the following items for all eligible companies:

- IP core RTL

- Standalone Simulation Environment

- Management SW

- IP Documentation

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about DDR IP core

The complete series of high-end DDR IP solutions of Innosilicon is industry-leading and across major foundry processes

Secure DDR DRAM Against Rowhammer, RAMBleed, and Cold-Boot Attacks

DDR IP Hardening - Overview & Advance Tips

Which DDR SDRAM Memory to Use and When

DDR5/4/3/2: How Memory Density and Speed Increased with each Generation of DDR

Frequently asked questions about DDR Controller IP cores

What is Memory Controller?

Memory Controller is a DDR IP core from OPENEDGES Technology, Inc. listed on Semi IP Hub.

How should engineers evaluate this DDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.