LPDDR5 PHY IP

Welcome to the ultimate LPDDR5 PHY IP hub! Explore our vast directory of LPDDR5 PHY IP

All offers in

LPDDR5 PHY IP

Filter

Compare

82

LPDDR5 PHY IP

from

11

vendors

(1

-

10)

-

LPDDR5X/5/4X/4 combo PHY at Samsung SF5A

- Compliant for JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

- x16 and x32 channel support

-

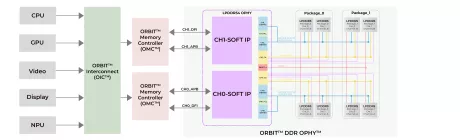

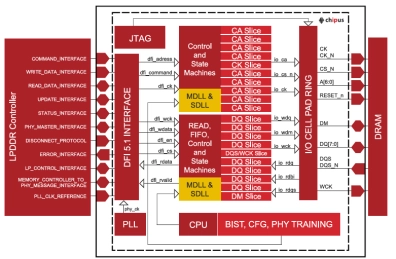

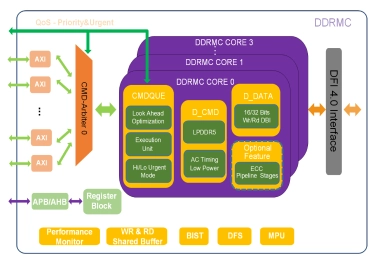

LPDDR5X/5/4X/4 PHY & Controller

- The LPDDR IP includes a LPDDR5X/5/4X/4 Combo PHY and controller.

- It is fully compliant with the JEDEC standard. Optimized for low-power and high-speed applications, it ensures robust timing and a small silicon area.

- The PHY IP contains specialized functions to guarantee high-performance I/Os, critical timing, low power and jitter with programmable fine-grain control for any SDRAM interface.

-

LPDDR5X/5/4X/4 combo PHY at 12nm

- Compliant with JEDEC JESD209-5C for LPDDR5x/5/4x/4 with PHY standards

- Delivering up to 8533Mbps

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

- Multiple frequency states

-

LPDDR5X/5/4X/4 PHY for 16nm

- Compliant with JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports up to 4 ranks

- Multiple frequency states

-

LPDDR5/4x/4 combo PHY on 14nm, 12nm

- Compliant with JEDEC standards for LPDDR5/4x/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports 1,2, or 4 ranks

- Multiple frequency states

-

LPDDR5/4x/4 PHY IP for Samsung 14LPU

- Compliant with JEDEC standards for LPDDR5/4x/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports 1,2, or 4 ranks

- Multiple frequency states

-

LPDDR4/4x/5/5x PHY

- Supports JEDEC SDRAM standards including LPDDR4 (1.1V), LPDDR4x (0.6V), LPDDR5/5x (0.5V)

- Supports data rates up to 4,266 Mbps LPDDR4/LPDDR5 and up to 8,533 Mbps LPDDR5x

- Support for 16, 32 and 64-bit operation

-

LPDDR5 IP solution

- Support LPDDR5 up to 6400Mbps

- Support Channel equalization with 1-tap DFE

- Support single-ended mode on CK, WCK and read DQS below 3200Mbps

- Support Link ECC for RDQS and DM

-

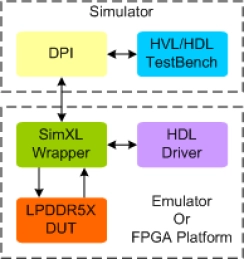

LPDDR5X Synthesizable Transactor

- Supports 100% of LPDDR5X protocol draft JEDEC specification and JESD209-5B specification.

- Supports all the LPDDR5X commands as per the specs.

- Supports device density up to 32GB.

- Supports X8 and X16 device modes.

-

LPDDR5 Synthesizable Transactor

- Supports 100% of LPDDR5 protocol standard JESD209-5, JESD209-5A and JESD209-5B.

- Supports all the LPDDR5 commands as per the specs

- Supports device density up to 32GB

- Supports X8 and X16 device modes