LDPC IP

Welcome to the ultimate LDPC IP hub! Explore our vast directory of LDPC IP

All offers in

LDPC IP

Filter

Compare

87

LDPC IP

from

20

vendors

(1

-

10)

-

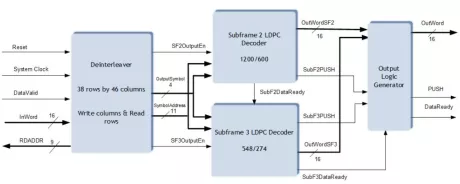

LunaNet AFS LDPC Encoder and Decoder IP Core

- Rate 1/2

- GNSS, AFS

- Subframe 2/3/4

- Low implementation loss

-

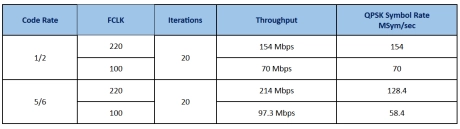

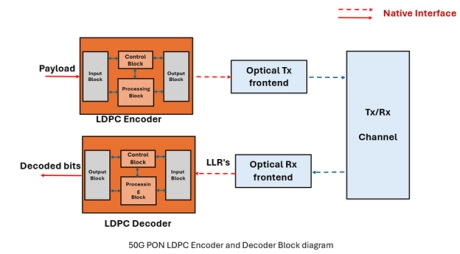

50G PON LDPC Encoder/Decoder

- Fully compliant with ITU-T G.9804 LDPC specifications

- Supports downstream and upstream FEC requirements - LDPC (17280, 14592)

- Supports Throughput up to 50 Gbps

- Supports both hard-decision and soft-decision decoding

-

SDA OCT Encoder and Decoder

- The SDA OCT Encoder handles the construction of Over-The-Air (OTA) frames as indicated in the standard, a preamble followed by a header and payload data, with both fields being protected by cyclic redundancy check (CRC) and forward error correction (FEC).

- The SDA OCT Decoder performs the synchronization of the Over-The-Air (OTA) frame and then decodes the header and payload data within the frame.

-

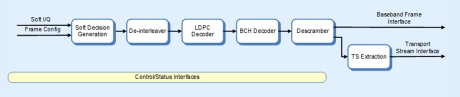

DVB-Satellite FEC Decoder

- The CMS0077 Satellite FEC Decoder has been designed specifically to meet the requirements of the DVB-S2 and DVB-S2X advanced wide-band digital satellite standards.

- The core provides all the necessary processing steps to convert a demodulated complex I/Q signal into a standard TS output stream.

-

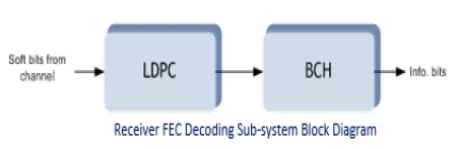

DVB-S2-LDPC-BCH IP

- Irregular parity check matrix

- Layered Decoding

- Minimum sum algorithm

- Soft decision decoding

-

LDPC Decoder IS-GPS-800D IP

- Irregular parity check matrix

- Layered Decoding

- Minimum sum algorithm

- Configurable number of iterations

-

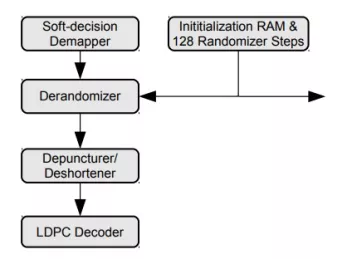

DOCSIS 3.1 LDPC Decoder (PLC / NCP / Data)

- Soft-Decision Demapper, Derandomizer, Deinterleaver, Depuncturer, and LDPC Decoder are included

- Support for 4k and 8K FFT sizes

- Support for 16-QAM modulation

-

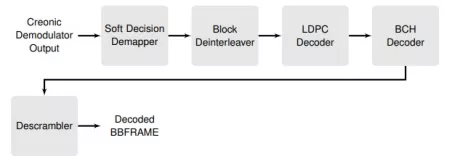

DVB-S2X Wideband BCH and LDPC Decoder

- Compliant with DVB-S2 and DVB-S2X

- Support for decoding of BBFRAMEs

- Support for ACM, CCM, and VCM

-

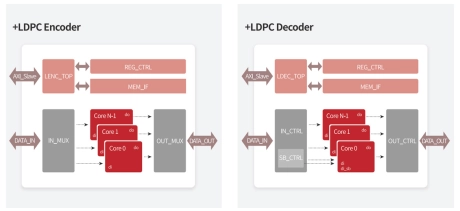

LDPC Encoder / Decoder

- Support 1KB+/2KB+/4KB+ codeword size for one time configuration

- Support code rate (CR) range 0.93~0.83(down to 0.71)

- Support configurable throughput, ranges from 300MB/s to 16GB/s

- Support hard-bit decode (HBD) and up to 6bit soft-bit decode (SBD)

-

DVB-S2-LDPC-BCH

- Irregular parity check matrix

- Layered decoding

- Minimum sum algorithm

- Soft decision decoding

- BCH decoder works on GF (2m) where m=16 or 14 and corrects up to t errors, where t = 8, 10 or 12