Turbocode IP

Welcome to the ultimate Turbocode IP hub! Explore our vast directory of Turbocode IP

All offers in

Turbocode IP

Filter

Compare

44

Turbocode IP

from

13

vendors

(1

-

10)

-

High bit rate Turbo Decoder core for 3GPP LTE/ LTE A

- 3GPP LTE/ LTE A compliant

- Implements decoder for requirements as defined in Section 5.1.3.2 of the specification

-

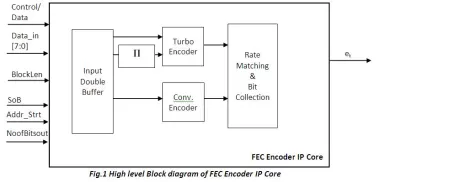

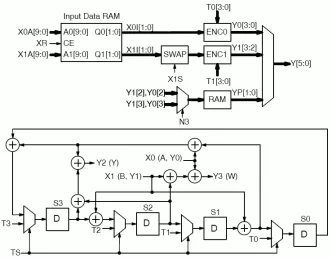

Complete FEC Encoder Solution compliant to LTE/ LTE A Specification

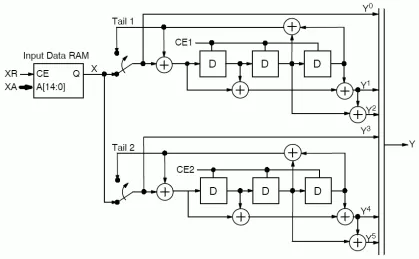

- Controlled selection of Turbo or Convolution path (based on data blocks input or control data input)

- Rate 1/3 tail biting Convolution encoder

- Rate 1/3 turbo encoder

- Rate matching for Turbo coded transport channels

-

Turbo Intel® FPGA IP

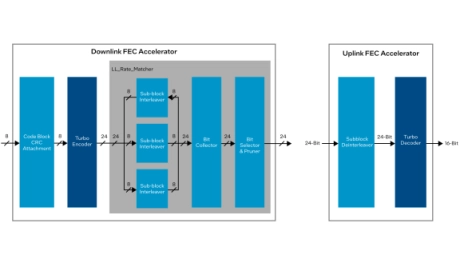

- Forward-error correction (FEC) channel codes commonly improve the energy efficiency of wireless communication systems

- Turbo codes are suitable for 3G and 4G mobile communications and satellite communications

- You can use Turbo codes in other applications that require reliable information transfer over bandwidth- or latency-constrained communication links in the presence of data-corrupting noise. The 4G Turbo-V Intel® FPGA IP comprises a downlink and uplink accelerator for vRAN and includes the Turbo Intel® FPGA IP.

-

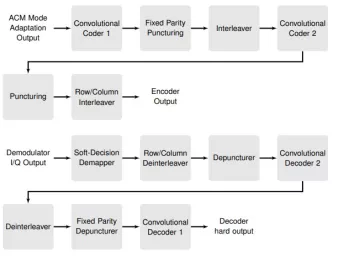

CCSDS SCCC Turbo Encoder and Decoder

- Burst-to-burst on-the-fly configuration

- High payload block length granularity (between 5,758 and 43,678 bits)

- High code rate granularity (code rates between 0.36 and 0.90)

- Configurable amount of turbo decoding iterations for trading off throughput and error correction performance

-

Inmarsat Compatible 16 State Turbo Encoder

- 16 state Inmarsat compatible turbo encoder

- Rate 1/2 to 1/5

- Data lengths from 8 to 32,764 bits

-

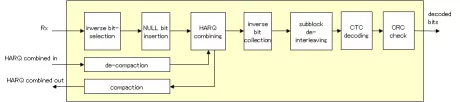

LTE Cat-0 turbo decoder

- Covers: Inverse rate matching, HARQ combining, CTC decoding, CRC check

- Maximal payload block size selectable at synthesis

-

High Speed Inmarsat Compatible Turbo Decoder

- Turbo Decoder:

- Viterbi Decoder (Optional):

- Available as VHDL core for AMD-Xilinx FPGAs under SignOnce IP License. ASIC, Intel/Altera, Lattice and Microsemi cores available on request.

-

16 state DVB-RCS2 Turbo Encoder

- 16 state DVB-RCS2 compatible

- Rate 1/3, 2/5, 1/2, 2/3, 3/4, 4/5, 5/6, 6/7, 7/8 with reverse output option

-

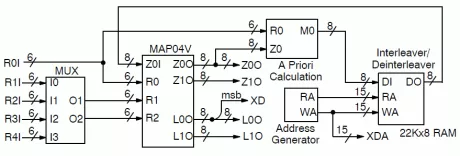

3GPP UMTS LTE 3GPP2 cdma2000 1xEV-DV 1xEV-DO Turbo Decoder with Optional Viterbi Decoder

- Turbo Decoder

- Viterbi Decoder (Optional)

- Available as VHDL core for Xilinx FPGAs under SignOnce IP License. ASIC, Altera, Lattice and Microsemi cores available on request.

-

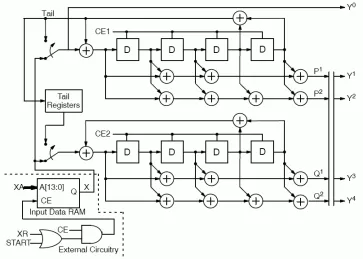

3GPP UMTS LTE 3GPP2 cdma2000 1xEV-DV 1xEV-DO 8 state turbo encoder

- 8 state 3GPP™ (UMTS and LTE) and 3GPP2 cdma2000 (1xEV-DV Release D and 1xEV-DO Release B) compatible turbo encoder

- Rate 1/2, 1/3, 1/4 or 1/5

- 40 to 5114 bit (3GPP™ UMTS), 40 to 6144 (3GPP™ LTE) or 17 to 32768 (3GPP2)

- Implement one, two or four different standards from the one core