Very Low Latency BCH Codec

These cores implement a Bose-Chaudhuri-Hocquenghem (BCH) error correction code configured to process a k-bit codeword, providing …

Overview

These cores implement a Bose-Chaudhuri-Hocquenghem (BCH) error correction code configured to process a k-bit codeword, providing the capability to correct up to t bit errors per block. On the decoder side, more than t errors will be typically detected with “uncorrectable” cff pin asserted.

The core targets the high-performance very-low-latency error correction ASIC applications with high k (about 500) and small t (3-5) using Bose–Chaudhuri–Hocquenghem codes (BCH codes) that prioritize latency over size. The performance of the BCH10 core is 1 word (k bits) per clock (that is, new codeword is produced or accepted on every clock). The clock rates of 2-3 GHz and more are possible in high-speed semiconductor technology nodes.

The latency of the encoder core is 2 clocks. The decoder latency is 5-7 clocks input-to-output data.

Key features

- High performance, low latency

- Small size (75K gates for k=298, t=4) configuration, the core uses just 17K gates in ASIC)

- Entirely self-contained (no external RAM required)

- Data inputs and outputs have flip-flops attached to the pins

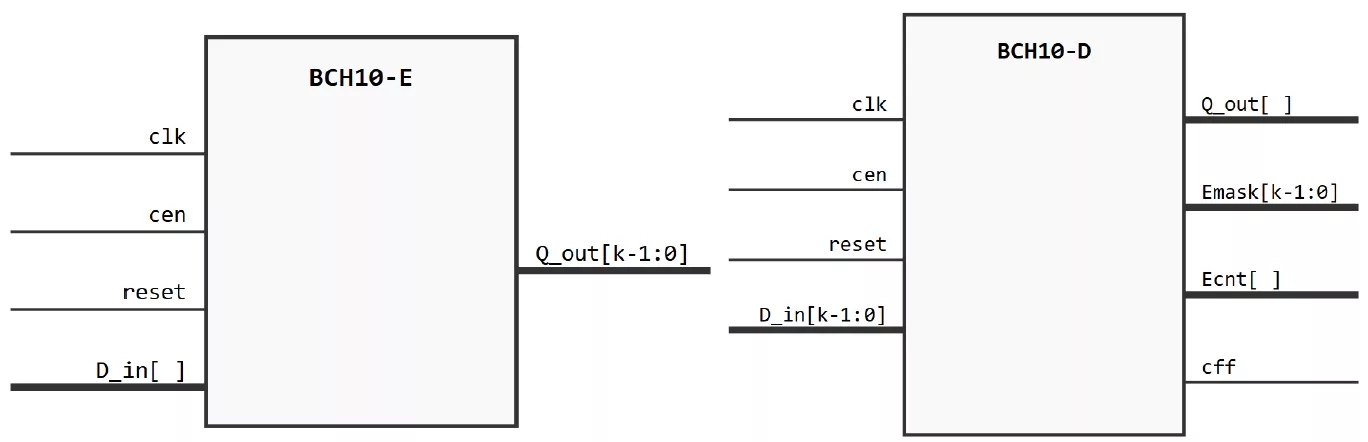

Block Diagram

What’s Included?

- Synthesizable Verilog RTL source code

- Test bench (self-checking)

- Test vectors

- Expected results

- Software Development Kit (SDK)

- User Documentation

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Channel Coding IP core

Altera purchases optical network IP vendor Avalon Microelectronics

FAUST: On-Chip Distributed SoC Architecture for a 4G Baseband Modem Chipset

Satellite modems structure Internet access

Audio Transport in DisplayPort VIP

Extending the SoC Architecture of 3G terminal to Multimedia Applications

Frequently asked questions about Channel Coding IP cores

What is Very Low Latency BCH Codec?

Very Low Latency BCH Codec is a Channel Coding IP core from IP Cores, Inc. listed on Semi IP Hub.

How should engineers evaluate this Channel Coding?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Channel Coding IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.