BCH IP

Welcome to the ultimate BCH IP hub! Explore our vast directory of BCH IP

All offers in

BCH IP

Filter

Compare

23

BCH IP

from

7

vendors

(1

-

10)

-

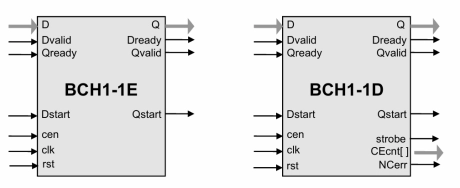

Very Low Latency BCH Codec

- High performance, low latency

- Small size (75K gates for k=298, t=4) configuration, the core uses just 17K gates in ASIC)

- Entirely self-contained (no external RAM required)

- Data inputs and outputs have flip-flops attached to the pins

-

Parameterizable compact BCH codec

- Highly parameterizable

- Very low area (in the largest, n = 511 t = 16 configuration, the core uses just 17K gates in ASIC)

- Entirely self-contained (no external RAM required)

-

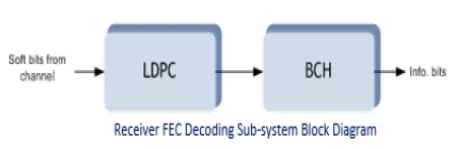

DVB-S2-LDPC-BCH IP

- Irregular parity check matrix

- Layered Decoding

- Minimum sum algorithm

- Soft decision decoding

-

-

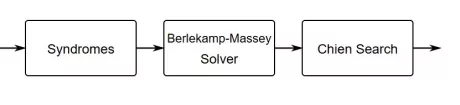

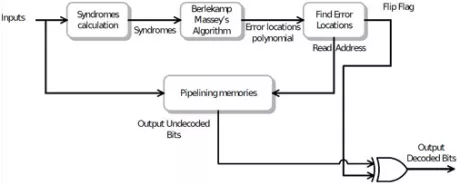

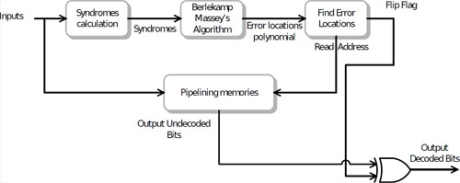

BCH Decoder IP

- BCH decoder compliant with the DVB-T2/S2 standard.

- Available for Altera/Xilinx FPGA or ASIC implementation.

- High speed design.

- BCH decoder works on GF(2M) where M = 16 or 14 and correctup to T errors where T = 10 or 12.

-

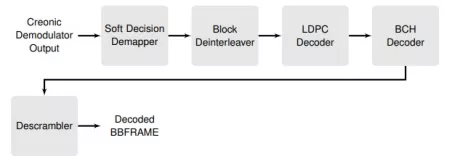

DVB-S2X Wideband BCH and LDPC Decoder

- Compliant with DVB-S2 and DVB-S2X

- Support for decoding of BBFRAMEs

- Support for ACM, CCM, and VCM

-

BCH Decoder

- BCH decoder compliant with the DVB-T2/S2 standard.

- Available for Altera/Xilinx FPGA or ASIC implementation.

- High speed design.

- BCH decoder works on GF(2M) where M = 16 or 14 and correctup to T errors where T = 10 or 12.

- Area and power optimized implementation.

-

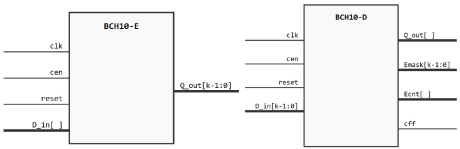

512B/ECC16 Nand Flash BCH Encoder/Decoder

- 2-16 bit error correction

- 2-900 data bytes per block

- Low-latency, synchronous design

- Pipelined correction operation supports 3 concurrent corrections

-

DVB-C2 Receiver (including LDPC and BCH decoder)

- Compliant with ETSI 302 769 (DVB-C2).

- Support for short blocks (16200 bits) and long blocks (64800 Bits).

- Support for all modulation schemes (16-QAM, 64-QAM, 256-QAM, 1024-QAM, 4096-QAM).

- Support for all interleaving schemes of all modulation schemes.

-

DVB-S2 BCH and LDPC Encoder and Decoder

- Compliant with ETSI 302 307 V1.2.1 (2009-08) (DVB-S2).

- Support for short blocks (16200 bits) and long blocks (64800 bits).

- Support for all modulation schemes (QPSK, 8-PSK, 16-APSK, 32-APSK).

- Support for all interleaving schemes of all modulation schemes.